# Extended family of DC-DC quasi-Z-source converters

# Muhammad Ado<sup>1</sup>, Awang Jusoh<sup>2</sup>, Tole Sutikno<sup>3</sup>

<sup>1,2</sup>School of Electrical Engineering, Universiti Teknologi Malaysia, Malaysia

<sup>1</sup>Department of Physics, Bayero Univerity, Nigeria

<sup>3</sup>Department of Electrical Engineering, Universitas Ahmad Dahlan, Indonesia

### **Article Info**

#### Article history:

Received Feb 5, 2019 Revised Mei 30, 2019 Accepted Jun 13, 2019

### Keywords:

Buck-boost DC-DC Impedance source q-ZSC Shoot-through

#### Corresponding Author:

Muhammad Ado, School of Electrical Engineering, Universiti Teknologi Malaysia, 81310 Skudai, Johor, Malaysia. Email: adobaffa@gmail.com

### ABSTRACT

The family of DC-DC q-ZSCs is extended from two to three classes and four to six members. All the members were analyzed based on efficient duty ratio range ( $R_{\rm Deff}$ ) and general duty ratio range ( $R_{\rm Deff}$ ). Findings showed that similar to the traditional buck-boost converter (BBC), each of the topologies is theoretically capable of inverted buck-boost (BB) operation for the  $R_{\rm Dgen}$  with additional advantages but differed according to class in how the gains are achieved. The new topologies have advantages of BB capability at the  $R_{\rm Deff}$ , continuous and operable duty ratio range with unity gain at D=0.5 contrary to existing topologies where undefined or zero gain is produced. Potential applications of each class were discussed with suitable topologies for applications such as fuel cells, photovoltaic, uninterruptible power supply (UPS), hybrid energy storage and load levelling systems identified.

Copyright © 2019 Institute of Advanced Engineering and Science.

All rights reserved.

4540

# 1. INTRODUCTION

Power converters convert electric energy from a magnitude or form to another [1, 2]. DC-DC converters convert between DC voltages, while ac-ac converters convert between ac-signals. DC-ac and ac-DC converters called inverters and rectifiers respectively convert between DC and ac signals. DC-DC converters are essential in applications involving DC signals of variable magnitudes. They generally involve using switches mostly transistors and are classified as linear or switched mode DC-DC converters depending on how the transistors are operated.

Linear mode converters involve operating the transistor at a given operating point in the linear region and regulation is achieved by varying the transistor base current  $(I_B)$  hence functions like a variable resistor [3]. In switched mode converters, transistors function as switches where they are switched ON/OFF based on their duty ratios (D). Linear mode converters are characterised by low efficiency while switched mode converters contain harmonics due to switching and require filters [4-8]. Switched mode converters were further classified into voltage source converters (VSCs) and current source converters (CSCs) until the invention of impedance source converters (ISCs/ZSCs) [9].

ISCs permits both the shoot-through (ST) limitation of VSCs without causing overcurrent for voltage boosting and open circuit (OC) limitation of CSCs without causing overvoltage for current boosting [9-13]. ST phenomenon is simultaneous switching of both switches of a common leg of an H-bridge while OC refers to turning them both OFF [14]. Dead-time and overlap-time are provided in VSCs and CSCs respectively to cater for ST and OC respectively but that causes waveform distortion and causes frequency restriction because the chances of ST or OC increases with frequency due to the possible interval becoming shorter [9, 15]. Elimination of dead and overlap-time in ISCs permits higher frequency operation leading to

reduced size, weight and cost [16]. Inductors of ISCs store energy during ST and release them during different modes while robustness of ISCs is that they can be controlled with or without ST [17-19].

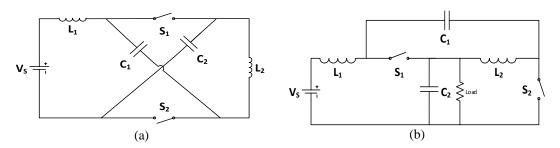

A derivative of the ZSCs called quasi-ZSC (q-ZSC) shown in Figure 1 (a) was proposed by [20] to address problems including discontinuous input current during boost mode, reduced source stress and simplified control strategy. Reference [21] extended the applications of ZSCs and q-ZSCs from dc-ac [9, 18, 22-35] and ac-ac [36] to DC-DC application by proposing four topologies each for ZSC and q-ZSC topologies. The extension to DC-DC was done by taking the output across a capacitor rather than switch  $S_2$  for both the dc-ac and ac-ac converters as shown in Figure 1 (b).

Both the DC-DC ZSC and q-ZSC families consisted of two classes each with each class comprising of two topologies. Derivation of variant topologies was possible due to the fact that the output could be taken across any capacitor and the positions of the input source and a capacitor could be swapped [21]. Other variant DC-DC converter topologies took their outputs across  $S_2$  in what is called pulse width modulated (PWM) DC-DC ISCs [37-43] for higher voltage gain albeit with additional components. Reference [44] took the DC output parallel to the impedance network input port rather than a capacitor or switch in order to achieve common ground and high voltage gain. Detailed steady-state analysis of PWM DC-DC ISCs was presented by [38].

DC-DC ISCs are further classified according to galvanic isolation into isolated and non-isolated [12, 45]. Topologies with transformer isolation usually have safety advantages and higher voltage gain but constrained by their relatively high cost and complexity, more switches requirement and low efficiency [45, 46]. Non-isolated DC-DC ISCs have advantages of low cost, less complexities and switches and higher efficiency but are constrained by safety problem and lower voltage gain [46].

The existing family of DC-DC q-ZSCs [21] with two classes has the advantage of bidirectional operation and bipolar output operation. However, each of the classes has problems of lacking buck-boost (BB) capability at efficient duty ratio range (R<sub>Deff</sub>) and either discontinuous or lower gain [47].

In this paper, a new class of DC-DC q-ZSCs is presented to extend the family of DC-DC q-ZSCs from two to three classes. Members of the new class have BB capability at the R<sub>Deff</sub>, continuous or higher gain compared to existing members. A general analysis of all the classes and their topologies is presented in details by first deriving the gain of each topology. Operations of all the classes were verified by simulation and the responses of Class B and Class C conform to their theoretical gains. The responses of Class C members disagreed with their theoretical gain due to the discontinuity in their gain.

Figure 1. (a) Generic q-ZSC (b) DC-DC q-ZSC

#### 2. OVERVIEW

# a) Existing topologies

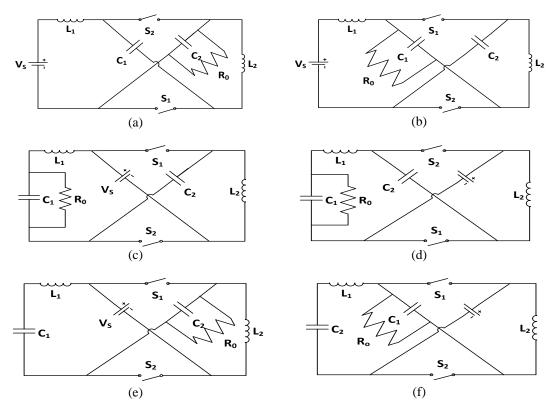

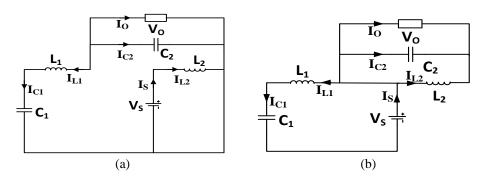

The concept q-ZSC was extended by [21] from inverter [20] to DC-DC applications. This produced four different topologies shown in Figure 2(a) to Figure 2(d) of which two of each have an identical gain curve. This lead to having two classes of DC-DC q-ZSC with each class consisting of two members [21]. Members of each class have an identical gain equation.

#### b) Additional topologies

Two new DC-DC converter topologies with the shared properties of q-ZSCs and traditional BBCs shown in Figure 2(e) and Figure 2(f) were recently proposed [2, 14]. Analysis of their operation shows common properties such as gain equation and output response, therefore, can be grouped as a class [47].

### c) Extended family

Combining the existing four DC-DC q-ZSC topologies and the two additional topologies result in having an extended family consisting of six members as shown in Figure 2. Of these six members, three gain curves exist, of which each consists of two members. This means that the extended family consists of three classes with each having two topologies [21, 47].

#### 3. CIRCUIT ANALYSIS

In this section, the operation of each class is analysed based on two operation modes to derive the gain equation of each topology in the class. Although ISCs can support more than two operation modes due to the permissibility of ST and OC, two operation modes were considered here because

- a. Existing analyses for the existing topologies [21] are based on two switching modes.

- Use of two switching modes enables fair comparison with other DC-DC topologies that only support two

modes.

Figure 2. Extended family of DC-DC q-ZSCs

The topologies in a class are labelled as topology I and topology II. The operation of each topology is analysed based on the switching modes and the equivalent circuits for each mode are also shown. The parameters used for the circuits analyses are  $V_{L1}$  (voltage across  $L_1$ ),  $V_{L2}$  (voltage across  $L_2$ ),  $V_{C1}$  (voltage across  $C_1$ ),  $V_{C2}$  (voltage across  $C_2$ ),  $V_0$  (output voltage),  $V_0$  (input voltage) and D (duty ratio). The switches  $S_1$  and  $S_2$  were assumed to be ideal.

# a) Class A

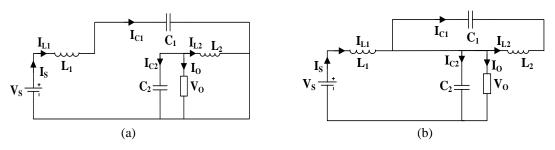

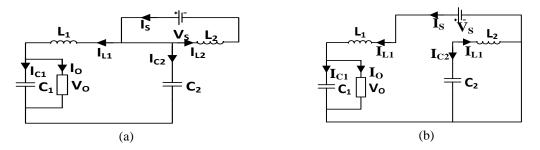

This class consist of the topologies of Figure 2(a) and (b) labelled as topology I and topology II and shown in Figure 3 and Figure 4 respectively.

Figure 3. Class A topology I (a) mode I (b) mode II

Figure 4. Class A topology II, (a) mode I (b) mode II

# 1. Class A topology I

Mode I: In this mode,  $S_1$  is ON while  $S_2$  is OFF as shown in Figure 3(a), the duty ratio is D.

$$V_{L1} = V_S - V_{C1} \tag{1}$$

$$V_{L2} = V_0 \tag{2}$$

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 3(b), the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_0 (3)$$

$$V_{L2} = V_{C1} \tag{4}$$

Applying Volt second balance (VSB) to get the average inductor voltages over a switching period on the inductors  $L_1$  and  $L_2$  yields (5) and (6).

$$\overline{V}_{L1} = -DV_{C1} + V_S - V_O + DV_O = 0$$

(5)

$$\overline{V}_{L2} = DV_0 + V_{C1} - DV_{C1} = 0$$

(6)

From (6),

$$V_{C1} = -\frac{DV_0}{1-D} \tag{7}$$

Substituting (7) into (5) and simplifying yields

$$A_{a1} = \frac{V_0}{V_S} = \frac{1 - D}{1 - 2D} \tag{8}$$

# 2. Class A topology II

Mode I: In this mode,  $S_1$  is ON while  $S_2$  is OFF as shown in Figure 4(a), the duty ratio is D.

$$V_{L1} = V_S - V_{C2} \tag{9}$$

$$V_{1,2} = V_0$$

(10)

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 4(b) the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_0 (11)$$

$$V_{L2} = V_{C2} \tag{12}$$

Applying VSB on L<sub>1</sub> and L<sub>2</sub> yields (13) and (14).

$$\overline{V}_{L1} = V_S - V_O + DV_O - DV_{C2} = 0 \tag{13}$$

$$\overline{V}_{L2} = DV_0 + V_{C2} - DV_{C2} = 0 \tag{14}$$

From (14),

$$V_{C2} = \frac{DV_0}{D-1} \tag{15}$$

Substituting (15) into (13) yields

$$A_{a2} = \frac{V_0}{V_S} = \frac{1 - D}{1 - 2D} \tag{16}$$

The (8) And (16) show that the ideal gains of topology I and II are identical as proposed by [21] thus they form a class with gain.

$$A_{a} = A_{a1} = A_{a2} = \frac{1-D}{1-2D} = \frac{D'}{D'-D}$$

(17)

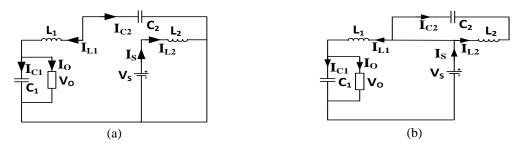

### b) Class B

The topologies in Figure 2(c) and (d) are members labelled as topology I and II and shown in Figure 5 and Figure 6 respectively.

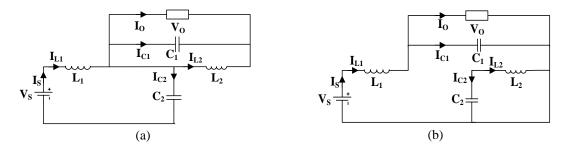

Figure 5. Class B topology I (a) mode I (b) mode II

Figure 6. Class B topology II (a) mode I (b) mode II

# 1. Family B topology I

Mode I: In this mode,  $S_1$  is ON while  $S_2$  is OFF as shown in Figure 5(a), the duty ratio is D.

$$V_{L1} = V_{C2} - V_0 (18)$$

$$V_{L2} = V_{S} \tag{19}$$

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 5(b), the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_0 (20)$$

$$V_{L2} = V_{C2}$$

(21)

Applying VSB on L<sub>1</sub> and L<sub>2</sub> yields (22) and (23).

$$\overline{V}_{L1} = DV_{C2} + V_S - V_O - DV_S = 0$$

(22)

$$\overline{V}_{L2} = DV_S + V_{C2} - DV_{C2} = 0$$

(23)

From (23),

$$V_{C2} = \frac{-D}{1-D}V_{S} \tag{24}$$

Substituting (24) into (22) and simplifying yields

$$A_{b1} = \frac{V_0}{V_S} = \frac{1 - 2D}{1 - D} \tag{25}$$

# 2. Class B topology II

Mode I: In this mode, S<sub>1</sub> is ON while S<sub>2</sub> is OFF as shown in Figure 6(a), the duty ratio is D.

$$V_{L1} = V_{C2} - V_0 \tag{26}$$

$$V_{L2} = V_S \tag{27}$$

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 6(b), the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_0 (28)$$

$$V_{L2} = V_{C2}$$

(29)

Applying VSB on L<sub>1</sub> and L<sub>2</sub> yields (30) and (31).

$$\overline{V}_{L1} = DV_{C2} + V_S - V_O - DV_S = 0 \tag{30}$$

$$\overline{V}_{L2} = DV_S + V_{C2} - DV_{C2} = 0 \tag{31}$$

From (31),

$$V_{C2} = \frac{-D}{1-D}V_{S} \tag{32}$$

Substituting (32) into (30) and simplifying yields

$$A_{b2} = \frac{V_0}{V_S} = \frac{1 - 2D}{1 - D} \tag{33}$$

The (25) And (33) show that the ideal gains of topology I  $A_{b1}$  and topology II  $A_{b2}$  are identical as proposed by [21] thus they form a class with gain.

$$A_b = A_{b1} = A_{b2} = \frac{1-2D}{1-D} = \frac{D'-D}{D'}$$

(34)

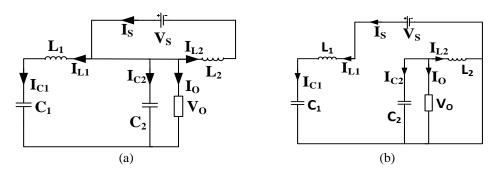

# c) Class C

This class consist of the two newly proposed topologies of Figure 2(e) and (f). They are also labelled as topology I and topology II as shown in Figure 7 and Figure 8 respectively.

Figure 7. Class C topology I (a) mode I (b) mode II

Figure 8. Class C topology II (a) mode I (b) mode II

# 1. Class C topology I

Mode I: In this mode,  $S_1$  is ON while  $S_2$  is OFF as shown in Figure 7(a), the duty ratio is D.

$$V_{L1} = V_0 - V_{C1} \tag{35}$$

$$V_{L2} = V_{S} \tag{36}$$

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 7(b), the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_{C1} \tag{37}$$

$$V_{L2} = V_0$$

(38)

Applying VSB on L<sub>1</sub> and L<sub>2</sub> yields (39) and (40).

$$\overline{V}_{L1} = DV_0 + V_S - V_{C1} - DV_S = 0$$

(39)

$$\overline{V}_{L2} = DV_S - V_O(D - 1) = 0 \tag{40}$$

Simplifying (40) yields

$$V_{O} = -\frac{D}{1-D}V_{S} \tag{41}$$

$$A_{c1} = \frac{V_0}{V_S} = \frac{-D}{1-D} \tag{42}$$

# 2. Class C topology Ii

Mode I: In this mode,  $S_1$  is ON while  $S_2$  is OFF as shown in Figure 7(a), the duty ratio is D.

$$V_{L1} = V_0 - V_{C1} \tag{43}$$

$$V_{L2} = V_{S} \tag{44}$$

Mode II: In this mode,  $S_1$  is OFF while  $S_2$  is ON as shown in Figure 7(b), the duty ratio is D' = 1 - D.

$$V_{L1} = V_S - V_{C1} \tag{45}$$

$$V_{1,2} = V_0$$

(46)

Applying VSB on  $L_1$  and  $L_2$  yields (47) and (48).

$$\overline{V}_{L1} = DV_0 + V_S - V_{C1} - DV_S = 0 \tag{47}$$

$$\overline{V}_{L2} = DV_S + V_O(1 - D) = 0 \tag{48}$$

Simplifying (48) yields

$$V_0 = -\frac{D}{1-D}V_S \tag{49}$$

$$A_{c2} = \frac{V_0}{V_S} = \frac{-D}{1-D} \tag{50}$$

The (42) And (50) show that the ideal gains of topology I  $A_{c1}$  and topology II  $A_{c2}$  are identical thus they form a class [47] with gain.

$$A_{c} = A_{c1} = A_{c2} = \frac{-D}{1-D} = \frac{-D}{D'}$$

(51)

The gain in (51) is the same as the gain of traditional BBC [2, 14].

The circuit analyses above show that the six topologies form three classes A, B and C with gains given by (17), (34) and (51) respectively for each class. Class A and class B have been previously presented [21]. The new class (class C), similar to the existing classes also consist of two topologies with identical gain equation, a quasi-impedance source network (q-ISN) comprising of two inductors, two capacitors and two switches.

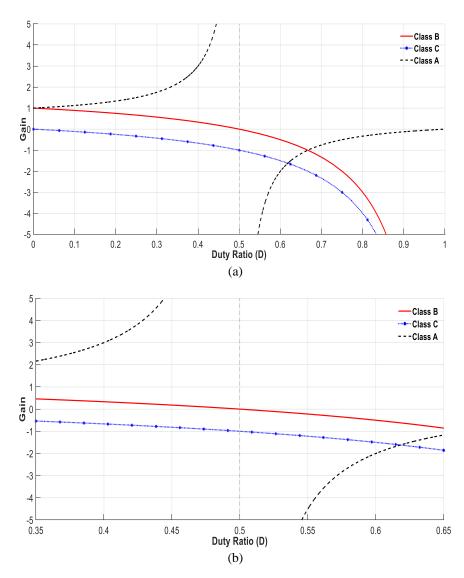

The gains of the three classes are plotted against D in Figure 9. The capacitor  $C_1$  and inductor  $L_1$  form a series LC network with impedance  $Z_1$  regardless of operating mode, contrary to the existing topologies where the series LC networks are formed only during given modes. This implies that the characteristics of the topologies will be altered when operated at their resonant frequencies due to resonance.

# 4. OPERATIONS AND APPLICABILITY

This section analyses the operations of each class as D is varied from 0 to 1. The D range  $(R_D)$  is classified into the efficient  $R_D$  (0.35 to 0.65) [12, 38, 48] and general  $R_D$  (0 to 1) thereby resulting in efficient gain range  $(R_{Aeff})$  and general gain range  $(R_A)$ . Suitable applications for each class are also discussed.

# a) Efficient duty ratio range $(R_{Deff})$

Operations of complementarily switched converters are more efficient at  $R_D$  of 0.35 to 0.65 due to less ringing, reverse recovery problem and conduction loss [12, 38, 48, 49]. This is because when either of the switches is operated at lower D, the other is at higher D (inverse D relationship) thus increasing conduction loss, ringing and other non-idealities [38]. The boundaries and midpoint of the efficient  $R_D$  ( $R_{Deff}$ ) were applied to the gain equations of these three classes to analyse their gains for the  $R_{Deff}$ . Figure 9(b) shows plots of the gains against D for  $R_{Deff}$ .

## 1. Class A

Applying the boundary and midpoint Ds of  $R_{\text{Deff}}$  to the gain equation of class A in (17), the resulting gains are

$$A_{a0.35} = \frac{1 - 0.35}{1 - 2(0.65)} = 2.1667 \tag{52}$$

$$A_{a0.5} = \frac{1-0.5}{1-2(0.5)} = \text{undefined}$$

(53)

$$A_{a0.65} = \frac{1 - 0.65}{1 - 2(0.35)} = -1.1667 \tag{54}$$

The (53) is undefined  $A_{a0.5} = \frac{0.5}{0}$  because division by zero is undefined. The concept of limit is applied to have more idea on what actually occurred as D  $\rightarrow$  0.5.

$$\lim_{D \to 0.5} A_a = \lim_{D \to 0.5} \frac{1 - D}{1 - 2D} \tag{55}$$

If the limit of the function exists at 0.5, then its two one-sided limits  $\lim_{D\to 0.5^+} A_a$  and  $\lim_{D\to 0.5^-} A_a$  must be equal else the limit does not exist.  $\lim_{D\to 0.5^+} A_a$  is the limit from the right as  $D\to 0.5$  while  $\lim_{D\to 0.5^-} A_a$  is the limit to the left as  $D\to 0.5$ .

The concept of right-sided limit (RSL) and left-sided limit (LSL) can be described using increasing and decreasing D in tuning. When a D set point is approached from a higher D such as bucking operation in traditional BBC, it is RSL (D  $\gtrsim$  0.5 such that D - 0.5 = 0<sup>+</sup>  $\Rightarrow$  2D  $\gtrsim$  1). When D is approached from a lower D such as boosting operation in traditional BBC, it is an LSL limit (D  $\lesssim$  0.5 such that D - 0.5 = 0<sup>-</sup>  $\Rightarrow$  2D  $\lesssim$  1). Evaluating the RSL and LSL yields

$$\lim_{D \to 0.5^+} A_a = +\infty \tag{56}$$

$$\lim_{D \to 0.5^{-}} A_a = -\infty \tag{57}$$

$$\lim_{D \to 0.5^{+}} A_a \neq \lim_{D \to 0.5^{-}} A_a \tag{58}$$

The (58) Shows that the one-sided limits are not identical therefore the limit does not exist at D = 0.5, thus the converter cannot be operated at D = 0.5. It shows that for this  $R_D$  (0.35 to 0.65), the gain is discontinuous at D = 0.5 because it's limit  $\lim_{D\to 0.5} A_a$  does not exist. The range of gain for class A ( $R_{Aa}$ ) corresponding to  $R_{Deff}$  with the RSL and LSL incorporated to account for the discontinuity is

$$R_{Aaeff} = [2.1667, \infty) (-\infty, -1.1667]$$

(59)

This discontinuity results in having two separate gains as shown by the two dotted curves of Figure 9(b) and the two ranges of (59). They are (i) non-inverting gain (upper dotted curve of Figure 9(b)) with range  $(R_{Aeff}) = [2.1667, \infty)$  and (ii) the inverting gain curve (lower dotted curve of Figure 9(b)) with range  $(R_{Aeff}) = [-1.1667, -\infty)$  described as non-inverting boost with gain from 2.1667 to  $\infty$  and inverting boost with gain from  $-\infty$  to -1.1667.

The theoretical gain for this class is bipolar with magnitude >1 throughout the  $R_{\rm Deff}$  hence it functions only as boost converter but lacks buck capability at this  $R_{\rm D}$ . Special precautions have to be taken to avoid operation within the neighbourhood of D=0.5 because of the infinite gain.

Applicability: For the positive boost range of (59),  $R_{Aa} = [2.1667, ∞)$  at  $R_D = [0.35, 0.5)$ . This high boost only capability makes the topologies in this class suitable for applications where voltage boosting is required like fuel cells. If the maximum input voltage magnitude is less than half the required output ( $|V_S| < 0.5 |V_O|$ ), the converter can be operated within [0.35, 0.5) with an ideal gain capability of  $10V_S$  at D = 0.4737, else it should be operated within (0.5, 0.65] duty ratio to get an inverted boost operation. By employing active switches (MOSFET) and their anti-parallel diodes, they are capable of providing bidirectional current and bidirectional voltage [21].

Suitable applications based on its theoretical gain include hybrid energy storage system (HESS) where energy may be transferred from battery to super-capacitor (SC) and vice versa [48], uninterruptible power supply (UPS) [49] and fuel cell application [9] where high gain is needed etc. However, simulation results obtained from the verification section raises doubt over the high boost capability. See the discussion section for more details.

# 2. Class B

Applying the boundary and midpoint Ds of  $R_{\text{Deff}}$  to the gain equation of class A in (17), the resulting gains are

$$A_{b0.35} = \frac{1 - 2(0.5)}{1 - (0.5)} = 0.4615 \tag{60}$$

$$A_{b0.5} = \frac{1 - 2(0.5)}{1 - (0.5)} = 0 \tag{61}$$

П

$$A_{b0.65} = \frac{1 - 2(0.35)}{1 - 0.65} = -0.8571 \tag{62}$$

The gain for this class is continuous, it exists at D=0.5 and is zero as shown in (61). The gain range is  $R_{Abeff}=[0.4615,-0.8571]$  and is bipolar with magnitude <1 hence it functions only as bipolar buck converter and lack boost capability within this  $R_{Deff}$  of 0.35 to 0.65.

Precautions have to be taken to handle the change in polarity that occurs at the neighbourhood of D = 0.5 because of the effect on power flow.

*Applicability:* Potential application could be in a grid-connected inverter system where the ESS is charged by a higher voltage source and the ESS later powers an inverter (load) at a lower voltage. Another application is in electric vehicle (EV) where ESS packs are designed in higher voltages e.g. 48 V than auxiliary loads such as lighting and radio systems which are operated at lower voltages of 12 or 24 V [50].

#### 3. Class C

Applying boundary and midpoint D of  $R_{\text{Deff}}$  to the gain equation of class C in (51), the resulting gains are

$$A_{c0.35} = -\frac{0.35}{1 - 0.35} = -0.5385 \tag{63}$$

$$A_{c0.5} = -\frac{0.5}{1 - 0.5} = -1 \tag{64}$$

$$A_{c0.65} = -\frac{0.65}{1 - 0.65} = -1.8571 \tag{65}$$

For members of this class, the gain is continuous and unity (= 1) at D = 0.5 as shown in (64),  $R_{Aeff} = [-0.5385, -1.8571]$ . Their gain is unipolar and inverting and can be  $\leq |1|$  thus has BB capability at this  $R_D$ . The gain is continuous and operable throughout the  $R_D$  hence requiring no precautionary measure. Contrary to class A and B, they are not capable of bidirectional operation by varying D [21, 45].

**Applicability:** They function as inverted BBCs by supplying an ideal output voltage that is 53.85 % of the input voltage in buck mode and up to 185.71 % of the input voltage in boost mode. A major advantage of this class is that they pose no control limitation within the duty ratio range.

Applications are similar to BBC applications with added advantages of dead and overlap-time elimination that permits higher frequency application and enables usage of smaller reactive components thus reducing size, weight and cost [16].

### b) Complete duty ratio range $(R_{dgen})$

Operations of the three classes are analysed beyond the  $R_{Deff}$  to identify other capabilities of the converters at all permissible D at the cost of reduced efficiency. Figure 9(a) shows a plot of the gains against D for  $R_{Dgen}$ .

# 1. Class A

Converters in this class are better analysed by considering their discontinuous gain as two separate curves as shown in Figure 9(a). The first (upper dotted) curve covers  $R_D$   $0 \le D < 0.5$ , it's  $R_A$  is  $1 \le A_a < \infty$ . The converter lacks buck capability. It functions as a non-inverting boost converter and is suitable for high boost operation. For the second curve, it covers the  $R_D$   $0.5 < D \le 1$  and has  $R_A$  as  $-\infty < A_a \le 0$  which implies unipolar inverted BB gain. In general, this class has a bipolar boost and unipolar BB capability.

*Applicability:* Reference [21] found that members of class A and B are capable of bi-directional energy transfer from source to load and vice versa thus permitting four quadrant operation by using active switches (MOSFETs and their antiparallel diode) as  $S_1$  and  $S_2$  by only varying D without using additional components. Special control precautions should be taken to avoid operation in the discontinuous regions. Potential applications are multimode circuits involving battery, SC or/and HESS) such as [50-53] or even in simple battery-inverter, uninterruptible power supply (UPS) and other load levelling systems where the battery may be charging, discharging or on standby [21, 54-56].

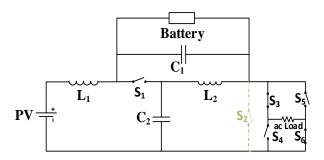

Another application is in PV distributed generation (DG) system [57] or in standalone PV system shown in Figure 10 where topology II shown in Figure 2(b) is modified by using PV output as supply with reverse blocking diode, a battery as load and replacing  $S_2$  with an inverter bridge.

# 2. Class B

Topologies in this class function as non-inverting buck converter for  $R_D$   $0 \le D < 0.5$  with  $R_A$   $1 \ge A_B > 0$  where  $A_B$  is the gain. For  $R_D$  0.5 < D < 1, they function as inverting BBC with  $|R_A|$  as  $|0 < A_B < \infty|$ . This implies that this class has bipolar buck and unipolar buck-boost capability when operated over the  $R_D$   $0 \le D < 1$  with gain  $-1 \le A_B < \infty$ .

Figure 9. Plot of gain vs. duty ratio for the three classes (a) general duty ratio range (b) complete duty ratio range

Figure 10. Class A topo. II with auxiliary H-bridge

- Applicability: They are suitable in bidirectional power transfer applications such as in HESS where ESS<sub>1</sub> (V<sub>S</sub>) voltage could be above or below ESS<sub>2</sub> (load) voltage [58]. They are also used as inverters by varying D from [0, 0.667] where the gain varies from [1, -1] to give an output voltage that varies from [V<sub>0</sub>, -V<sub>0</sub>] and the output voltage range of the inverter is the same as that of the full-bridge single-phase semi-Z-source and semi-quasi-Z-source inverters [45].

#### 3. Class C

The gain for this class is the same as that of traditional BBC hence they have unipolar inverting BB capability when D is varied within  $R_D$  0 < D < 1 with gain range as  $0 < A_C < \infty$ . Their advantage over the two-switch and four-switch BBC is the elimination of ST and OC in the gate control signal thus permitting higher frequency operations.

- *Applicability:* The operation over R<sub>Dgen</sub> is the general application and is similar to the efficient application because BB operation can be achieved in both applications unlike in the other classes. The major difference is that the gain is extended for the general application from [−0.5385, −1.8571] to [0, −∞]. Suitable application is unidirectional BB operation with wide input or output variation.

Although the number of capacitors (dual) and inductors (dual) may be thought of as disadvantage compared to traditional BBC, but BBCs with single capacitors also employ additional input capacitor [48] while the two inductors could be coupled together [11, 22, 46, 59]. Also, the capacitor and inductor requirements of ISCs are smaller due to second order filtering [9], high-frequency application permissibility also allows the use of smaller components and the non-output side components more smaller when asymmetric components are used [60].

#### 5. VERIFICATION, RESULTS AND DISCUSSIONS

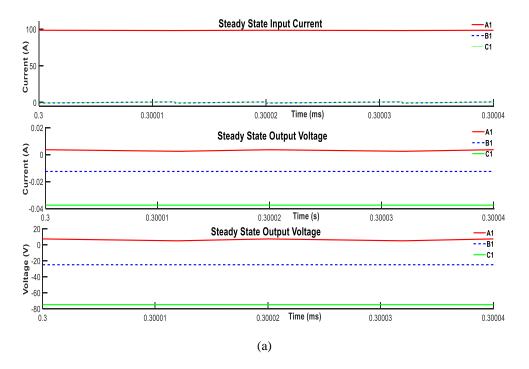

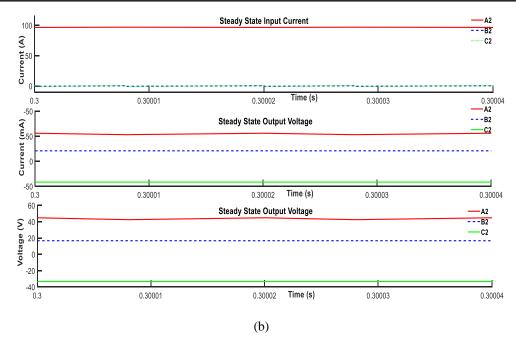

Operations of corresponding ideal symmetric converters from the three classes with parameter values given in Table 1 were simulated using MATLAB SIMULINK and compared for D=0.6 and D=0.4 to verify their operations. Topologies I for all the classes were used for D=0.6 while topologies II were used for D=0.4. Their responses are shown in Figure 11 (a) and Figure 11 (b) respectively.

| Table 1. Parameter values for the ideal symmetric q-ZSCs used |                |     |    |       |       |       |       |  |  |  |  |

|---------------------------------------------------------------|----------------|-----|----|-------|-------|-------|-------|--|--|--|--|

| Parameter                                                     | V <sub>g</sub> | f   | Ro | $C_1$ | $C_2$ | $L_1$ | $L_2$ |  |  |  |  |

| Unit                                                          | V              | KHz | ΚΩ | μF    | μF    | μН    | μН    |  |  |  |  |

| Value                                                         | 50             | 50  | 2  | 500   | 500   | 400   | 400   |  |  |  |  |

Figure 11. Simulation response of the Classes at (a) D = 0.6

Figure 11. Simulation response of the Classes at (b) D = 0.4

Responses of the family shown in Figure 11 (a) and Figure 11 (b) exposes the limitations of class A caused by the discontinuity in its gain. This is because from the ideal gain (17), the output voltages of for D = 0.6 and 0.4 should be

$$V_{O(D=0.6)} = \frac{1-0.6}{1-2(0.6)} \times 50 = -100 \text{ V}$$

(66)

$$V_{O(D=0.4)} = \frac{1-0.4}{1-2(0.4)} \times 50 = 150 \text{ V}$$

(67)

These values are far away from the 7 V in the result of Figure 11 (a) and 45 V of Figure 11 (b) which are both below  $V_{\rm g}$  as shown in Table 2. It signifies lack of boost capability and implies that the high boost application discussed in section IV may not be achievable.

Table 2. Comparison of ideal and simulation responses

| 2 440      | Tueste 2: Comparison of fueur and simulation responses |         |    |         |      |      |  |  |  |  |  |  |

|------------|--------------------------------------------------------|---------|----|---------|------|------|--|--|--|--|--|--|

| Duty Ratio |                                                        | D = 0.6 |    | D = 0.4 |      |      |  |  |  |  |  |  |

| Class      | A                                                      | В       | С  | A       | В    | С    |  |  |  |  |  |  |

| Ideal      | 100                                                    | -25     | 75 | 150     | 16.7 | 33.3 |  |  |  |  |  |  |

| Simulation | 7                                                      | -25     | 75 | 45      | 16.7 | 33.3 |  |  |  |  |  |  |

Response of class B and C are in agreement with their theoretical gains as given in Table 2 thereby making them practically realizable. This also indicates that only Class C members are capable boost operation at  $0.4 \le D \le 0.6$ .

The ideal gain of each class is unique and the same for its members. Advantages and disadvantages between class members can be identified using their dynamic models [60]. Possible operating parameters should be first analysed before selecting the class to use for a given operation because each class has its pros and cons over other classes.

It is also important to note that class A and B each have one topology with common ground between input and output while the other topology has floating output. For class C, all the two topologies have floating output. Topologies with common ground have advantages over those with floating output in transformer-less applications due to leakage current [44, 45].

The higher number of capacitors and inductors shouldn't be discouraging compared to traditional DC-DC converters with single capacitor because

- a. Non-impedance source DC-DC converters employ additional input capacitor [48] while the two inductors could be coupled together.

- b. The capacitor and inductor requirements of ISCs are smaller due to second order filtering by the network [9].

- c. High-frequency operation permissibility allows the use of smaller and asymmetric components [60].

- d. Existing high gain non-impedance source DC-DC converter topologies have higher components count [46, 49].

- e. Non-impedance source bidirectional DC-DC converters use additional components.

- f. ISCs can also function with single capacitor [61].

### 6. CONCLUSION

An extended family of non-isolated DC-DC q-ZSCs with three classes has been presented. Operation of each class was analysed based on the efficient ( $R_{Deff}$ ) and general duty ratio range ( $R_{Dgen}$ ) to identify potential applications. Findings showed that similar to the traditional BBC, each of the topologies is capable of inverted buck-boost (BB) operation for the ( $R_{Dgen}$ ).

#### REFERENCES

- [1] Y. P. Siwakoti, F. Z. Peng, F. Blaabjerg, P. C. Loh, G. E. Town, and S. Yang., "Impedance-source networks for electric power conversion part II: Review of control and modulation techniques," *IEEE Trans. Power Electron.*, vol. 30(4), pp. 1887-1906, 2015.

- [2] M. Ado, A. Jusoh, M. J. A. Aziz, M. Kermadi, and A. U. Mutawakkil., "DC-DC q-ZSC with Buck-Boost Converter Gain," in 9th IEEE Control and System Graduate Research Colloquium, pp. 85-88, 2018.

- [3] D. W. Hart., Power Converters. New York: M Graw-Hill, 2011.

- [4] K. Mainali and R. Oruganti, "Conducted EMI Mitigation Techniques for Switch-Mode Power Converters: A Survey," vol. 25(9), pp. 2344-2356, 2010.

- [5] Z. Yang and P. C. Sen, "DC-to-DC Buck Converter with Novel Current Mode Control," *Power Electron. Spec. Conf. 1999. PESC 99. 30th Annu. IEEE*, vol. 00(1), pp. 1158-1164, 1999.

- [6] Z. Yang and P. C. Sen, "A novel switch-mode DC-to-AC inverter with nonlinear robust control," *IEEE Trans. Ind. Electron.*, vol. 45(4), pp. 602-608, 1998.

- [7] Z. Yang and P. C. Sen, "Analysis of a novel bidirectional dc-to-ac inverter," *IEEE Trans. Circuits Syst. I Fundam. Theory Appl.*, vol. 47(5), pp. 747-757, 2000.

- [8] M. C. Cavalcanti, F. Bradaschia, M. T. de Melo Neto, G. M. S. Azevedo, and T. D. Cardoso., "Dynamic modeling and control system design of the buck-boost-based three-state three-phase Z-source inverter," *Int. J. Electr. Power Energy Syst.*, vol. 104, pp. 654-663, 2019.

- [9] F. Z. Peng., "Z-source inverter," *IEEE Trans. Ind. Appl.*, vol. 39(2), pp. 504-510, 2003.

- [10] P. C. Loh, F. Gao, and F. Blaabjerg., "Embedded EZ-Source Inverters," *IEEE Trans. Ind. Appl.*, vol. 46(1), pp. 256-267, 2010.

- [11] W. Qian, F. Z. Peng, and H. Cha., "Trans-Z-Source Inverters," IEEE Trans. Power Electron., vol. 26(12), pp. 3453-3463, 2011.

- [12] A. Chub, D. Vinnikov, F. Blaabjerg, and F. Z. Peng., "A review of galvanically isolated impedance-source DC-DC converters," *IEEE Trans. Power Electron.*, vol. 31(4), pp. 2808-2828, 2016.

- [13] W. Mo, P. C. Loh, and F. Blaabjerg., "Asymmetrical Γ-Source Inverters," *IEEE Trans. Ind. Electron.*, vol. 61(2), pp. 637-647, 2014.

- [14] M. Ado, A. Jusoh, S. M. Ayob, M. H. Ali, and G. S. M. Galadanchi., "Buck-Boost Converter with q-ZSC Topology," in 5th IET International Conference on Clean Energy and Technology, 2018.

- [15] Z. Yang and P. C. Sen, "Bidirectional DC-to-AC inverter with improved performance," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 35(2), pp. 533002D542, 1999.

- [16] C. M. C. Duarte and I. Barbi, "An improved family of ZVS-PWM active-clamping DC-to-DC converters," in PESC Record - IEEE Annual Power Electronics Specialists Conference, vol. 1, pp. 669-675, 1998.

- [17] Y. Li, S. Jiang, J. G. Cintron-Rivera, and F. Z. Peng., "Modeling and control of quasi-z-source inverter for distributed generation applications," *IEEE Trans. Ind. Electron.*, vol. 60(4), pp. 1532-1541, 2013.

- [18] M. Shen and F. Z. Peng, "Operation modes and characteristics of the Z-source inverter with small inductance or low power factor," *IEEE Trans. Ind. Electron.*, vol. 55(1), pp. 89-96, 2008.

- [19] C. J. Gajanayake, D. M. Vilathgamuwa, and P. C. Loh., "Development of a comprehensive model and a multiloop controller for Z-source inverter DG systems," *IEEE Trans. Ind. Electron.*, vol. 54(4), pp. 2352-2359, 2007.

- [20] J. Anderson and F. Z. Peng, "Four quasi-Z-Source inverters," in 2008 IEEE Power Electronics Specialists Conference, pp. 2743-2749, 2008.

- [21] D. Cao and F. Z. Peng, "A Family of Z-source and Quasi-Z-source DC-DC Converters," 2009 Twenty-Fourth Annu. IEEE Appl. Power Electron. Conf. Expo., pp. 1097-1101, 2009.

[22] M. Shen, A. Joseph, Y. Huang, F. Z. Peng, and Z. Qian., "Design and Development of a 50kW Z-Source Inverter for Fuel Cell Vehicles," in 5th ICES/EEE International Power Electronics and Motion Control Conference, 2006.

- [23] S. Yang, Q. Lei, F. Z. Peng, R. Inoshita, and Z. Qian., "Current-fed quasi-Z-source inverter with coupled inductors," 2009 IEEE Energy Convers. Congr. Expo. ECCE 2009, pp. 3683-3689, 2009.

- [24] Y. Huang, M. Shen, F. Z. Peng, and J. Wang., "Z-source inverter for residential photovoltaic systems," *IEEE Trans. Power Electron.*, vol. 21(6), pp. 1776-1782, 2006.

- [25] F. Z. Peng, X. Yuan, X. peng Fang, and Z. Qian., "Z-source inverter for adjustable speed drives," *IEEE Power Electron. Lett.*, vol. 99(2), pp. 33-35, 2003.

- [26] P. C. Loh, D. M. Vilathgamuwa, Y. Sen Lai, G. T. Chua, and Y. Li., "Pulse-width modulation of Z-source inverters," *IEEE Trans. Power Electron.*, vol. 20(6), pp. 1346-1355, 2005.

- [27] J. Liu, J. Hu, and Longya Xu., "A Modified Space Vector PWM for Z-Source Inverter Modeling and Design," in 8th International Conference on Electrical Machines and Systems, vol. 2, pp. 1242-1247, 2005.

- [28] S. Yang, X. Ding, F. Zhang, F. Z. Peng, and Z. Qian., "Unified Control Technique for Z-Source Inverter," in 2008 IEEE Power Electronics Specialists Conference, pp. 3236-3242, 2008.

- [29] J. Anderson and F. Z. Peng, "A class of quasi-Z-source inverters," in *Industry Applications Society Annual Meeting*, 2008. 2008. IAS '08. IEEE, pp. 1-7, 2008.

- [30] F. Z. Peng, M. Shen, and K. Holland., "Application of Z-Source Inverter for Traction Drive of Fuel Cell Battery Hybrid Electric Vehicles," *IEEE Trans. Power Electron.*, vol. 22(3), pp. 1054-1061, 2007.

- [31] M. Shen, Q. Tang, and F. Z. Peng., "Modeling and controller design of the Z-source inverter with inductive load," *PESC Rec. IEEE Annu. Power Electron. Spec. Conf.*, 2007, pp. 1804-1809.

- [32] X. Ding, Z. Qian, S. Yang, B. Cui, and F. Z. Peng., "A high-performance Z-source inverter operating with small inductor at wide-range load," *Conf. Proc. IEEE Appl. Power Electron. Conf. Expo. APEC*, 2007, pp. 615-620.

- [33] M. Shen, J. Wang, A. Joseph, F. Z. Peng, L. M. Tolbert, and D. J. Adams., "Maximum constant boost control of the Z-source inverter," *39th IEEE/IAS Ind. Appl. Conf.*, vol. 1(I), pp. 142-147, 2004.

- [34] U. Supatti and F. Z. Peng, "Z-source inverter based wind power generation system," 2008 IEEE Int. Conf. Sustain. Energy Technol., pp. 634-638, 2008.

- [35] Y. Li, J. Anderson, F. Z. Peng, and D. Liu., "Quasi-Z-Source Inverter for Photovoltaic Power Generation Systems," Appl. Power Electron. Conf. Expo. 2009. APEC 2009. Twenty-Fourth Annu. IEEE, 2009, pp. 918-924.

- [36] X. P. Fang, Z. Qian, and F. Z. Peng., "Single-Phase Z-Source PWM AC-AC Converters," *IEEE Power Electron. Lett.*, vol. 3(4), pp. 121-124, 2005.

- [37] I. Roasto, D. Vinnikov, T. Jalakas, Z. Janis, and S. Ott., "Experimental Study of Shoot-Through Control Methods for qZSI-Based DC/DC Converters," Int. Symp. Power Electron. Electr. Drives, Autom. Motion, pp. 293-296, 2010.

- [38] V. P. Galigekere and M. K. Kazimierczuk, "Analysis of PWM Z-source DC-DC converter in CCM for steady state," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 59(4), pp. 854-863, 2012.

- [39] J. Zakis, D. Vinnikov, O. Husev, and I. Rankis., "Dynamic behaviour of qZS-based bi-directional DC/DC converter in supercapacitor charging mode," SPEEDAM 2012 21st Int. Symp. Power Electron. Electr. Drives, Autom. Motion, pp. 764-768, 2012.

- [40] M. Egorov, D. Vinnikov, R. Strzelecki, and M. Adamowicz., "Impedance-Source Inverter-Based High-Power DC/DC Converter for Fuel Cell Applications," in *Proceeding 8th International Conference Environment and Electrical Engineering*, 2009, pp. 1-4.

- [41] D. Vinnikov, I. Roasto, and T. Jalakas., "New Step-Up DC / DC Converter with High-Frequency Isolation," in 35th Annual Conference of IEEE Industrial Electronics, 2009, pp. 670-675.

- [42] I. Roasto, D. Vinnikov, J. Zakis, and O. Husev., "New shoot-through control methods for qZSI-based DC/DC converters," *IEEE Trans. Ind. Informatics*, vol. 9(2), pp. 640-647, 2013.

- [43] D. Vinnikov and I. Roasto, "Quasi-Z-Source-based isolated DC/DC converters for distributed power generation," *IEEE Trans. Ind. Electron.*, vol. 58(1), pp. 192-201, 2011.

- [44] H. Shen, B. Zhang, D. Qiu, and L. Zhou., "A Common Grounded Z-Source DC-DC Converter With High Voltage Gain," *IEEE Trans. Ind. Electron.*, vol. 63(5), pp. 2925-2935, 2016.

- [45] D. Cao, S. Jiang, X. Yu, and F. Z. Peng., "Low-Cost Semi-Z-source Inverter for Single-Phase," *IEEE Trans. Power Electron.*, vol. 26(12), pp. 3514-3523, 2011.

- [46] F. Evran and M. T. Aydemir, "Isolated high step-Up DC-DC converter with low voltage stress," *IEEE Trans. Power Electron.*, vol. 29(7), pp. 3591-3603, 2014.

- [47] M. Ado, A. Jusoh, A. U. Mutawakkil, and S. M. Ayob., "Two q-ZSCs with Efficient Buck-Boost Gain," in 10th IEEE PES Asia-Pacific Power and Energy Engineering Conference, pp. 252-256, 2018.

- [48] C. Wang, R. Xiong, H. He, X. Ding, and W. Shen., "Efficiency analysis of a bidirectional DC/DC converter in a hybrid energy storage system for plug-in hybrid electric vehicles," *Appl. Energy*, vol. 183, pp. 612-622, 2016.

- [49] R. J. Wai, C. Y. Lin, C. Y. Lin, R. Y. Duan, and Y. R. Chang., "High-efficiency power conversion system for kilowatt-level stand-alone generation unit with low input voltage," *IEEE Trans. Ind. Electron.*, vol. 55(10), pp. 3702-3714, 2008.

- [50] B. Wang, J. Xu, B. Cao, and B. Ning., "Adaptive mode switch strategy based on simulated annealing optimization of a multi-mode hybrid energy storage system for electric vehicles," *Appl. Energy*, vol. 194, pp. 596-608, 2017.

- [51] W. Jing, C. H. Lai, W. S. H. Wong, and M. L. D. Wong., "A comprehensive study of battery-supercapacitor hybrid energy storage system for standalone PV power system in rural electrification," *Appl. Energy*, vol. 224, pp. 340-356, 2018.

- [52] B. Wang, J. Xu, R. J. Wai, and B. Cao., "Adaptive Sliding-Mode with Hysteresis Control Strategy for Simple Multimode Hybrid Energy Storage System in Electric Vehicles," *IEEE Trans. Ind. Electron.*, vol. 64(2), pp. 1404-1414, 2017.

- [53] Y. Zhan, Y. Guo, J. Zhu, and L. Li., "Power and energy management of grid/PEMFC/battery/supercapacitor hybrid power sources for UPS applications," *Int. J. Electr. Power Energy Syst.*, vol. 67, pp. 598-612, 2015.

- [54] K. Hirachi, M. Yamanaka, K. Kajiyama, and S. Isokane., "Circuit configuration of bidirectional DC/DC converter specific for small scale load leveling system," in *Power Conversion Conference-Osaka 2002*, *PCC-Osaka 2002*, vol. 2, pp. 603-609, 2002.

- [55] M. Yamanaka, M. Sakane, and K. Hirachi., "Practical Development of a High-Performance UPS with a Novel Buck-Boost Chopper Circuit," *INTELEC. Twenty-Second International Telecommunications Energy Conference*, pp. 632-637, 2000.

- [56] M. Kloess and K. Zach, "Bulk electricity storage technologies for load-leveling operation An economic assessment for the Austrian and German power market," *Int. J. Electr. Power Energy Syst.*, vol. 59, pp. 111-122, 2014.

- [57] D. Sun, B. Ge, D. Bi, and F. Z. Peng., "Analysis and control of quasi-Z source inverter with battery for grid-connected PV system," *Int. J. Electr. Power Energy Syst.*, vol. 46(1), pp. 234-240, 2013.

- [58] A. M. Florez-tapia, J. Vadillo, and J. M. Echeverria., "Electrical Power and Energy Systems Fault tolerance of the bidirectional trans quasi-Z-source inverter," *Int. J. Electr. Power Energy Syst.*, vol. 95, pp. 440-450, 2018.

- [59] F. Z. Peng., "Z-source networks for power conversion," in 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, pp. 1258-1265, 2008.

- [60] M. Ado, A. Jusoh, A. U. Mutawakkil, and T. Sutikno., "Dynamic model of a DC-DC quasi-Z-source converter (q-ZSC)," *Int. J. Electr. Comput. Eng.*, vol. 9(3), pp. 1585-1597, 2019.

- [61] A. R. Dehghanzadeh, V. Behjat, and M. R. Banaei., "Double input Z-source inverter applicable in dual-star PMSG based wind turbine," *Int. J. Electr. Power Energy Syst.*, vol. 82, pp. 49-57, 2016.

### **BIOGRAPHIES OF AUTHORS**

**Muhammad Ado** was born in Kaduna Nigeria in 1984. He received B.S. and M.S. degrees in Electronics from Bayero University, Kano, Nigeria in 2009 and 2016 respectively. He is currently pursuing his Ph.D. degree in Electrical engineering at Universiti Teknologi Malaysia. From 2010 to 2012 he was an external and panel operator at Kaduna Refining and Petrochemical Company limited. Since 2012, he has been with Bayero University, Kano as a graduate assistant and later lecturer. His research interests include power converters, modelling and semiconductor physics. Mr. Ado is a member of IEEE and NIP (Nigerian Institute of Physics).

Awang Jusoh was born in Terengganu, Malaysia in 1964. He received his B. Eng. (Hons) from Brighton Polytechnic, UK, in 1988. He obtained his MSc. and PhD. From The University of Birmingham, UK in 1995 and 2004, respectively. Since 1989, he has been a lecturer at Universiti Teknologi Malaysia and is now an Associate Professor at the Department of Power Engineering, School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia, Malaysia. His research interests include all areas of power electronics systems and renewable energy.

**Tole Sutikno** is an Associate Professor in Electrical & Computer Engineering Department Universitas Ahmad Dahlan, Yogyakarta, Indonesia. He receives B.Eng.; M.Eng; and Ph.D. degrees in 1999, 2004 and 2016 respectively. He has over 198 publication to his credit. His research interest in is the power electronics, motor drives, industrial electronics, Industrial application, FPGA application, intelligence control and Industrial informatics