ISSN: 2088-8708, DOI: 10.11591/ijece.v9i3.pp1757-1764

# CMOS ring oscillator delay cell performance: a comparative study

D. A. Hadi<sup>1</sup>, A. Z. Jidin<sup>2</sup>, N. Ab Wahab<sup>3</sup>, Madiha Z.<sup>4</sup>, Nurliyana Abd Mutalib<sup>5</sup>, Siti Halma Johari<sup>6</sup>, Suziana Ahmad<sup>7</sup>, M. Nuzaimah<sup>8</sup>

1.2.5.6.7 Department of Electronics and Computer Engineering Technology, Universiti Teknikal Malaysia Melaka, Malaysia

4.8 Department of Manufacturing Engineering Technology, Universiti Teknikal Malaysia Melaka, Malaysia

3 Department of Electrical Engineering Technology, Universiti Teknikal Malaysia Melaka, Malaysia

### **Article Info**

## Article history:

Revised Aug 11, 2018 Revised Nov 20, 2018 Accepted Dec 11, 2018

## Keywords:

Current starved Ring oscillator Voltage controlled oscillator

### **ABSTRACT**

A common voltage-controlled oscillator (VCO) architecture used in the phase locked loop (PLL) is the ring oscillator (RO). RO consist of number of inverters cascaded together as the input of the first stage connected to the output of the last stage. It is important to design the RO to be work at desired frequency depend on application with low power consumption. This paper presents a review the performance evaluation of different delay cell topologies the implemented in the ring oscillator. The various topologies analyzed includes current starved delay cell, differential delay cell and current follower cell. Performance evaluation includes frequency range, frequency stability, phase noise and power consumption had been reviewed and comparison of different topologies has been discussed. It is observed that starved current delay cell have lower power consumption and the different of the frequency range is small as compared to other type of delay cell.

Copyright © 2019 Institute of Advanced Engineering and Science.

All rights reserved.

1757

## Corresponding Author:

D. A. Hadi,

Department of Electronics and Computer Engineering Technology, University Technical Malaysia Melaka,

1, Jalan TU 43, Taman Tasik Utama 75450 Ayer Keroh, Melaka, Malaysia.

Email: dayanasari@utem.edu.my

## 1. INTRODUCTION

Basically, oscillator is a frequency translation that translate information signal with time reference. There is variation of oscillator with different principle operation, frequency oscillation and its noise performance. For instant, voltage-controlled oscillator (VCO) is one type of oscillator that output oscillation frequency can be varied by varying the amplitude of its input signal. There are two architectures of VCO namely; the ring oscillator and the LC oscillator.

Ring oscillator is widely used in the communication system design especially in the wireless ssystem [1]–[5] and FPGA application [6], [7] because of its wide tuning range, making them more robust over process and temperature variations. It also use used to study the degradation of logic CMOS circuit [8], [9]. Many trade-offs in terms of speed, power, area and application domain need to be considered in designing a ring oscillator. Thus, it is important to determine accurate frequency oscillation of the ring oscillator so that the designer able to make informed decisions regarding these trade-offs.

This paper is organized as follows. Section 2 discuss the basic concept of ring oscillator and the equations related to oscillation frequency that have been derived in previous works. In Section 3 investigates the available delay topologies used ring oscillator. Section 4 compares the performance and discuss the advantage and disadvantages of each topology. Section 5 presents our conclusions.

## 2. BASIC CONCEPT OF RING OSCILLATOR

Basically, ring oscillator is comprised of an odd number of NOT gates whose output oscillates between two voltage levels, representing '1' and '0'. The NOT gate is cascade in chain where the output of the last stage fed back to the input of the first. The oscillation can be achieved when circuit provide phase shift of  $2\pi$  and unity voltage gain at the oscillation frequency. Each delay stage must provide a phase shift of  $\pi/N$ , where N is the number of delay stages[10]. The remaining  $\pi\square$  phase shift is provided by a DC inversion. The most basic ring oscillator is simply a chain of single ended digital inverters because they have better thermal noise performance than their differential CMOS counterparts and can achieve better phase-noise performance for a given power dissipation [11], [12].

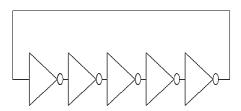

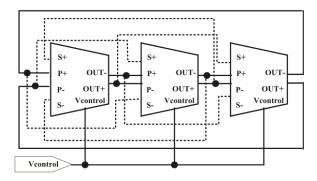

Figure 1 shows a block diagram of 5 stage ring oscillator that constructed by 5 inverters. In this ring oscillator, the output of each inverter is used as input for the next one and the last output is fed back to the input of the first inverter. Ring oscillator is commonly used in the process technology development to characterize the process performance[6], [8], [13], [14]. It also widely uses as clock generator, voltage controlled oscillator [15]–[18] and phase locked loop [19], [20].

First, let the output of the first inverter is a low indicate by '0' and its transfer the signal to the input of the second inverter. We know that an inverter will invert the input signal that pass through it. So, the second inverter's output must switch to a high condition indicates as '1'. This is how the oscillator oscillate its signal through the N number of stages implies in the circuit. The output of last inverter will transfer its signal to the input of the first inverter. This process will repeat indefinitely, resulting in the voltage at each node oscillating.

One of the important parameter of the ring oscillator is its oscillation frequency ( $f_{osc}$ ) that depends on the number of stages (n) and the delay time ( $t_d$ ) of each stage as expressed in (1) [10], [18], [21]. The oscillation frequency depends on the delay time of each stage consider the propagation delay for both transition low-to-high ( $t_{pLH}$ ) and high-to-low ( $t_{pHL}$ ). The delay occurs due to the time taken by the transistor gate capacitance to charge before current can flow from source to drain. Thus, the output of every unit changes after a certain amount of time after the input has changed. As the number of stages increase the total delay increases and hence the output frequency decreases. When all the individual units are made up of identical circuits, the delay due to one unit can be calculated by dividing the total delay with the number of stages.

$$f_{OSC} = \frac{1}{2\pi t_d} \tag{1}$$

Figure 1. The block diagram of five stage ring oscillator [17], [22]

## 3. TYPE OF DELAY CELL IN RING OSCILLATOR

## 3.1. Current starved delay cell based voltage controlled ring oscillator

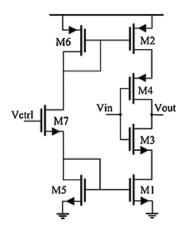

In real time, the supply voltage, VDD of a ring oscillator circuit varies and the voltage variation produce an output frequency variation. Thus, current is needed to be supply at each inverter to ensure the output frequency is stable. This can be done by using current starved inverter as shown in Figure 2, whereby it controls the amount of current to charge and discharge the capacitive load each stage. M1 and M2 operates as current source that limits the current through M3 and M4. M3 and M4 is an inverter and now it is said starved for current. The input control voltage controls the current of M5 and M6 and the values are mirrored in each inverter or current source voltage.

Figure 3 shows a current starved delay cell implemented in the voltage-controlled ring oscillator. It consists of five stages of ring oscillator whereby NMOS transistor work as current sources and the two PMOS transistor used in the delay cell. A current limiter circuit denotes by M1 and M13 is required in this type of structure such that it can limit the current through PMOS inverter. The tuning range of the circuit is

Int J Elec & Comp Eng

improved, the frequency linearity is increases and the power consumption is reduced when implementing this delay cell [22].

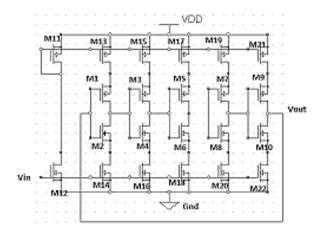

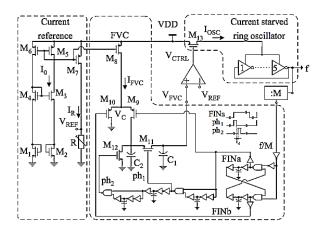

Besides, Niko and Adrijan had implemented current starved delay five stage current starved ring oscillator [23] as shown in Figure 4. The current variation in this circuit is almost zero when  $V_{RF}=V_{FVC}$  and thus the oscillation frequency is stable and independent of current variation. In this circuit, the current  $I_{osc}$  is never be zero to ensure the safe starts and the frequency of the oscillator is depending on the current value. Thus, this delay cell independent of the current variation and it is temperature dependent.

Figure 2. The current starved inverter [18], [24]

Figure 3. The schematic current starved delay cell based voltage controlled ring oscillator [22]

Figure 4. Circuit level Implementation of current staved ring oscillator based on the feedback loop architecture [23]

## 3.2 Differential delay cell

Another famous topology is the differential delay cell as illustrates in Figure 5. Basically, there are 2 delay paths in this circuit. The normal delay path, the differential output delay stage connects to the input of the next stage of the primary loop. Meanwhile, the skewed delay path is connected to secondary loop input of the next-second stage. This skewed delay path reduces delay time and phase noise of the circuit [23]. This type of delay cell preserves the high speed and low noise performance [25]. A differential four stage dual delay-path ring oscillated had been presented in [26] with two stable operation mode. The use of differential inverter delay stages has advantages over the use of single-ended delay stages, primarily because there is little distortion in the output [27].

The parameters that affect the frequency oscillation is given by (2). By varying tail current in delay stage,  $I_{SS}$  and peak-to-peak amplitude of the voltage waveform,  $V_{SW}$  the oscillation frequency is voltage controlled with constant load capacitance,  $C_L$ , number of stages, n, and delay of each stage in the ring oscillator, t. To the first order,  $V_{SW}$  increases as the  $I_{SS}$  increases and the frequency remains constant. Also,

it is often desirable to maintain a constant voltage swing during operation because if the swing is small, it increases the jitter, and if the swings are large, a higher supply voltage is needed for differential operation.

$$f_{osc} = \frac{I_{SS}}{2ntC_L V_{SW}} \tag{2}$$

It is reported that the ring oscillators based on a differential delay stage are very popular due to their immunity to disturbances on the supply line [28]. The phase noise of the differential ring oscillator has been investigated in [23], [29]-[32]. However, as technology scales, the timing jitter effect will become prominent because the transistor operate between saturation and triode mode and not taken into consideration in [23], [29].

Figure 5. Multiple-pass loop structure of three stage ring oscillator with differential delay [25]

## 3.3 Source follower delay cell

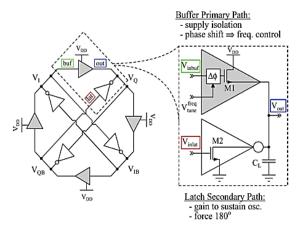

The frequency of the ring oscillator depends on the device parameter and its voltage supply. As we know that the ring oscillator that implemented in the digital circuit application require high speed logic switching. Thus, noise on the voltage supply line need to take into consideration in designing the ring oscillator. A source follower delay cell proposed to reject the supply even without calibration or other additional regulation as shown in Figure 6 [33]. This delay cell isolates the supply through the transistor output resistance and reduce supply sensitivity. Supply isolation is provided by the primary source follower path through M1 meanwhile voltage gain is provided by inverting-latch secondary path through M2. It is necessary to sustain oscillation forcing complementary node to be out of 180° out of phase. By adjusting differential tuning voltage, the frequency is controlled by the phase-shift/bias network.

Power dissipation increases when using low-dropout regulator due to the higher supply voltage and extra circuitry. In [34], both power and ground noises are isolated by using a differential supply-regulated tuning technique. Another method uses a source follower to couple the control voltage directly to a differential pair in place of a DC current source, which makes the biasing less robust.

Figure 6. A conceptual block diagram of ring oscillator with source follower delay cell [35]

#### 4. COMPARISON STUDY OF EACH TOPOLOGY

It is reported that the current starved gives better frequency linearity [36] and the oscillation of the frequency is device parameter and process dependent [22]. However, the oscillator does not require a stable current to obtain frequency that independent of voltage and temperature variation [37] due to the negative feedback in the oscillator. The power consumption is a bit higher as reported in [22] and to minimize the power consumption of the oscillator, the number of stages N, supply voltage  $V_{dd}$  and tail current  $I_{tail}$  should all be minimized [2], [37], [33], [34]. The current starved voltage-controlled oscillator improved jitter by adding D flip flop in the circuit [36]. A jitter is a variation of the reference signal with respect to ideal position in time and the impacts the data transmission quality [2].

In order to achieve better control voltage and frequency range for low voltage and wide tuning range voltage-controlled ring oscillator a new differential delay cell with complementary current control has been developed in [25]. Higher control voltage increases the current of each stage and decreases the delay time of each stage, and thus, increases the oscillation frequency [31], [38]. The differential delay cell able to reduce flicker noise contribution to the phase noise in the ring oscillator circuit by maximizing the number of stage [39] and thus channel length of the device need to be reduce. This lead to higher leakage current due to the short channel effect occur in the device. This problem can be reduced by using different type of device technology. A work presented in [40] proposed Double-gate (DG) FinFETs, the second gate is added opposite the traditional (first) gate, which have been recognized for their potential to better control short-channel effects (SCE) and as well as to control leakage current.

Basically, in this paper three type of delay cells implemented in the ring oscillator circuit is discussed in the Section III. The performance of the ring oscillator can be evaluated by measuring its oscillation frequency or frequency range, phase noise and power dissipation. A comparison parameters of different delay cell for ring oscillator is tabulated in Table 1. Each delay cell implemented in the ring oscillator has their own advantages and disadvantage thus it is important to know what the purpose and goal is in designing the circuits. From Table 1 it can be concluded that current starved delay cell is preferable to be use in the ring oscillator circuit due to its low power consumption compare to differential delay cell.

Table 1. Parameter Comparison Based On the Type of Delay Circuit Implemented in Ring Oscillator

| Delay Circuit<br>Type             | Current Starved Delay |               |              |                     | Differential Delay Cell               |                 |                                                            |                             |                                   | Source<br>Follower<br>delay cell           |

|-----------------------------------|-----------------------|---------------|--------------|---------------------|---------------------------------------|-----------------|------------------------------------------------------------|-----------------------------|-----------------------------------|--------------------------------------------|

| Year [publication]                | 2015<br>[22]          | 2013<br>[37]  | 2013         | 2012<br>[41]        | 2012 [39]                             | 2012            | 2011 [26]                                                  | 2011<br>[25]                | 2009<br>[42]                      | 2012                                       |

| Technology (nm)                   | 180                   | 180           | [36].<br>180 | 180                 | 350                                   | [4]<br>180      | 180                                                        | 180                         | 130                               | [3 <i>5</i> ]<br>90                        |

| Number of<br>Stages               | 5                     | 5             | 3            | 3                   | 3                                     |                 | 4                                                          | 3                           | 2                                 | -                                          |

| Supply<br>Voltage (v)             | 2.5                   | 1.2           | 1.8          | 1.8                 | 3                                     | 1.8             | -                                                          | 1                           | 1.3                               | -                                          |

| Oscillation<br>Frequency<br>(mhz) | -                     | -             | -            | 100 &<br>150        | -                                     | -               | -                                                          | -                           | -                                 | -                                          |

| Frequency                         | 0.00132               | 0.00<br>384 – | 0.53         |                     |                                       |                 |                                                            |                             |                                   |                                            |

| Range (ghz)                       | 0.00326               | 0.003<br>80   | 2.348        | -                   | -                                     | -               | -                                                          | -                           | -                                 | -                                          |

| Tuning Range (ghz)                | 69.11                 | -             | -            | -                   | -                                     | 3.125<br>- 5.26 | 1.77 - 1.92                                                | 0.479 -<br>4.09             | 1.82 –<br>10.18                   | 0.63 –<br>8.1                              |

| Phase Noise                       | -                     | -             | -            | -                   | 0.076<br>Magnitude<br>or -11.19<br>dB | -               | -102<br>dBc/Hz @<br>1 MHz,<br>-123.4<br>dBc/Hz @<br>10 MHz | -93<br>dBc/Hz<br>@ 1<br>MHz | -121.7<br>dBc/Hz<br>@ 5.6-<br>GHz | -106 to -<br>88<br>dBc/Hz<br>at 10-<br>MHz |

| Power (mw)                        | 0.0042                | 0.005<br>1    | 0.848        | 0.437<br>&<br>0.537 | -                                     | 0.621           | ~ 13                                                       | 13                          | 5                                 | 7 - 26                                     |

| Area (mm²)                        | -                     | 0.009         | -            | -                   | -                                     | -               | 0.002214                                                   | 0.00807<br>72               | -                                 | -                                          |

## 5. CONCLUSION

This paper presented a comparative study of delay cell in the ring oscillator includes starved current delay cell, differential delay cell and current follower cell. The discussions are based on the design parameters and technology process variation in the recent research of ring oscillator for low voltage application. In conclusion, it is observed that starved current delay cell have lower power consumption and the different of the frequency range is small compared to other two type of delay cell as presented in Table 1. This type of delay cell can be implemented in  $0.18 \, \mu m$  CMOS technology.

## **ACKNOWLEDGEMENTS**

The author would like to thanks Universiti Teknikal Malaysia Melaka (UTeM) and the Malaysia Ministry of Higher Education for the financial funding under grant no. FRGS/1/2015/TK04/FTK/03/F00285.

#### REFERENCES

- [1] Lee W. H. *et al.* "Oscillation-controlled CMOS Ring Oscillator for Wireless Sensor Systems," *Microelectronics Journal*, vol. 41(12), pp. 815–819.

- [2] Thakare A. P and V. Ramekar U, "Design and Analysis of Frequency Synthesizer with Low Power Ring Oscillator for Wireless Application," *Green Computing Communication and Electrical Engineering (ICGCCEE)*, 2014 International Conference on. IEEE. Coimbatore, pp. 1–6, 2014.

- [3] J. Jalil, et al. "CMOS Differential Ring Oscillators," IEEE Microwave Magazine, pp. 97–109, 2013.

- [4] A. Raman, et al. "A RF Low Power 0 .18-µm based CMOS Differential Ring Oscillator," In: Proceedings of the World Congress on Engineering, pp. 4–8, 2012.

- [5] D. Rani and S. M. Ranjan, "A 2.4 GHz Voltage Controlled Oscillator for Wireless Communication in CMOS Technology," *Int J Electron Commun Comput Technol*, vol. 2(3), pp. 115–119, 2012.

- [6] C. Ruething, et al. "Exploration of Ring Oscillator Design Space For Temperature Measurements on FPGAS," In: Field Programmable Logic and Applications (FPL), 2012 22nd International Conference on. Oslo: IEEE, pp. 559–62, 2012.

- [7] F. Kodytek and R. Lorencz, "A Design of Ring Oscillator Based PUF on FPGA," In: 2015 IEEE 18th International Symposium on Design and Diagnostics of Electronic Circuits & Systems, Belgrade, pp. 37–42, 2015.

- [8] J. Wang, *et al*, "Hot-Carrier Degradation Analysis based on Ring Oscillators," *Microelectron Reliab.*, vol. 46 (9-11), pp. 1858–1863, 2006.

- [9] A. Kerber, et al. "Fast Wafer-Level Stress-and-Sense Methodology for Characterization of Ring-Oscillator Degradation in Advanced CMOS Technologies," *IEEE Trans Electron Devices*, vol. 62(5), pp. 1427–32, 2015.

- [10] A. Tah and R. D. Kumar, "Study of The Frequency Characteristics of a Ring Oscillator," *Int J Comput Netw Technol*, vol. 1(3), pp. 171–183, 2013.

- [11] T. H. Lee and A. Hajimiri, "Oscillator Phase Noise: A Tutorial," in *IEEE Journal of Solid-State Circuits*, vol. 35(3), pp. 326-336, Mar 2000.

- [12] A. Hajimiri, *et al.*, "Jitter and phase noise in ring oscillators," in *IEEE Journal of Solid-State Circuits*, vol. 34(6), pp. 790-804, Jun 1999.

- [13] T. T. Kim, *et al.*, "A Ring-Oscillator-Based Reliability Monitor for Isolated Measurement of NBTI and PBTI in High-k/Metal Gate Technology," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23(7), pp. 1360-1364, Jul 2015.

- [14] T. T. Kim, et al., "Design of ring oscillator structures for measuring isolated NBTI and PBTI," *IEEE International Symposium on Circuits and Systems*, Seoul, pp. 1580-1583, 2012.

- [15] Z. Chen and T. Lee, "The Study of a Dual-Mode Ring Oscillator," in *IEEE Transactions on Circuits and Systems II:* Express Briefs, vol. 58(4), pp. 210-214, Apr 2011.

- [16] X. Lei, et al., "Design and Analysis of a Three-Stage Voltage-Controlled Ring Oscillator," Journal of Semiconductor, vol. 34(11), pp. 1-6, 2013.

- [17] S, Suman, et al. "An Improved Performance Ring Oscillator Design," In: Advanced Computing & Communication Technologies (ACCT), 2012 Second International Conference on, Rohtak, Haryana, pp. 236–239, 2012.

- [18] A. Ramazani, et al, "CMOS Ring Oscillator with Combined Delay Stages," *International Journal of Electronic and Communication*, vol. 68(6), pp. 515–519, 2014.

- [19] K. R. Lakshmikumar, "Analog PLL Design With Ring Oscillators at Low-Gigahertz Frequencies in Nanometer CMOS: Challenges and Solutions," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 56(5), pp. 389-393, May 2009.

- [20] O. Elhadidy, et al., "A Wide-Band Fully-Integrated CMOS Ring-Oscillator PLL-Based Complex Dielectric Spectroscopy System," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 62(8), pp. 1940-1949, Aug. 2015

- [21] M. Alioto and G. Palumbo, "Oscillation frequency in CML and ESCL ring oscillators," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48(2), pp. 210-214, Feb. 2001.

- [22] M. Bhardwaj and S. Pandey, "Design and Performance Analysis of Wideband CMOS Voltage Controlled Ring Oscillator," 2nd International Conference on Electronics and Communication Systems (ICECS), Coimbatore, pp. 142-145, 2015.

- [23] H. Q. Liu, et al., "A Low-Noise Multi-GHz CMOS Multiloop Ring Oscillator With Coarse and Fine Frequency Tuning," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 17(4), pp. 571-577, 2009.

- [24] B. Sadegh, et al., "Delay Time Analysis of Combined CMOS Ring Oscillator," Electrical and Electroic Engineering: An International Journal (ELELIJ), vol. 4(2), 2015.

- [25]M.-L. Sheu, et al., "A 1-V 4-GHz Wide Tuning Range Voltage-Controlled Ring Oscillator in 0.18μm CMOS," Microelectronics Journal, vol 42(6), pp. 897–902, 2011.

- [26] Z. Chen and T. Lee, "The Design and Analysis of Dual-Delay-Path Ring Oscillators," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58(3), pp. 470-478, Mar 2011.

- [27] H. Ghonoodi, et al., "Analysis of Frequency and Amplitude in CMOS Differential Ring Oscillators," Integration, the VLSI Journal, vol. 52, pp. 253-259, 2015.

- [28] B. Leung, "Design and Analysis of Saturated Ring Oscillators Based on the Random Mid-Point Voltage Concept," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21(8) pp. 1554-1557, Aug. 2013.

- [29] A. A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillators," in *IEEE Journal of Solid-State Circuits*, vol. 41(8), pp. 1803-1816, Aug. 2006.

- [30] Y. A. Eken and J. P. Uyemura, "A 5.9-GHz voltage-controlled ring oscillator in 0.18-/spl mu/m CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 39(1), pp. 230-233, Jan 2004.

- [31] B. Leung, "A Switching-Based Phase Noise Model for CMOS Ring Oscillators Based on Multiple Thresholds Crossing," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57(11), pp. 2858-2869, Nov. 2010.

- [32] L. S. de Paula, et al., "A Wide Band CMOS Differential Voltage-Controlled Ring Oscillator," Joint 6th International IEEE Northeast Workshop on Circuits and Systems and TAISA Conference, Montreal, pp. 9-12, 2008.

- [33] M. Lont, et al., "Requirement Driven Low-Power LC and Ring Oscillator Design," *IEEE International Symposium of Circuits and Systems (ISCAS)*, Rio de Janeiro, pp. 1129-1132, 2011.

- [34] B. Ghafari, et al., "An Ultra-Low-Power and Low-Noise Voltage-Controlled Ring Oscillator for Biomedical Applications," *IEEE 2013 Tencon* Spring, Sydney, NSW, pp. 20-24, 2013.

- [35] Pankratz EJ et al. "Multiloop High-Power-Supply-Rejection Quadrature Ring Oscillator," IEEE J Solid-State Circuits. vol. 47(9), pp. 2033–48, 2012.

- [36] M. Kulkarni and K. N Hosur, "Design of a Linear and Wide Range Current Starved Voltage Controlled Oscillator for PLL," *International Journal on Cybernetics & Informatics*, vol. 2(1), pp. 23-30, 2013.

- [37] N. Bako and A. Baric, "A Low-Power, Temperature and Supply Voltage Compensated Current Starved Ring Oscillator," *Microelectronics Journal*, vol. 44(12), pp. 1154–1158, 2013.

- [38] T. Wu, et al., "An On-chip Calibration Technique for Reducing Supply Voltage Sensitivity in Ring Oscillators," in *IEEE Journal of Solid-State Circuits*, vol. 42(4), pp. 775-783, April 2007.

- [39] T. Cronin, et al., "Complements on phase noise analysis and design of CMOS ring oscillators," 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2012), Seville, pp. 793-796, 2012.

- [40] A. L. Deepak, e al., "Designing of FinFET Based 5-Stage and 3-Stage Ring Oscillator High Frequency Generation in 32nm," *IEEE-International Conference On Advances In Engineering, Science And Management (ICAESM - 2012)*, Nagapattinam, Tamil Nadu, pp. 222-227, 2012.

- [41] S. Panyai and A. Thanachayanont, "Design and realization of a process and temperature compensated CMOS ring oscillator," 9th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Phetchaburi, pp. 1-4, 2012.

- [42] F, Bassem, et al., "A Two-Stage Ring Oscillator in 0.13-um CMOS for UWB Impulse Radia," *IEEE Transaction on Microwave Theory and Technique*, vol. 57(5), pp. 1074-1082, 2009.

## **BIOGRAPHIES OF AUTHORS**

**Dayanasari Abdul Hadi** was born in Kuala Lumpur, Malaysia. She received the bachelor's degree in electrical engineering from University of Malaya, Kuala Lumpur, Malaysia in 2006 and Master of Science in Microelectronics from Universiti Kebangsaan Malaysia. She was a CAD Development Engineer in National Semiconductor where she works on developing Process Design Kit. She is currently work as Teaching Engineer in UTeM and doing research under Micro and Nano Electronics (MINE).

**Aiman Zakwan Jidin** obtained his MEng in Electronic and Microelectronic System Engineering from ESIEE Engineering Paris France in 2011. He has 2 years of working experience in designing digital IC and digital system in FPGA at Altera Corporation Malaysia, before joining Universiti Teknikal Malaysia Melaka (UTeM) as lecturer and researcher, in Electronics and Computer.

1764 □ ISSN: 2088-8708

**Dr. Norfariza binti Ab Wahab** was born in Melaka, Malaysia. Undergraduate (2007-2009) and Master (2010-2012) from Nagaoka University of Technology, Niigata Japan from Department of Mechanical Engineering. She graduated from Tokyo University of Agriculture and Technology (2012-2015) for her PhD under Department of Mechanical System Engineering. She is currently work as senior lecturer at Universiti Teknikal Malaysia Melaka (UTeM) and her research interest mainly in manufacturing/machining as an additive manufacturing and high efficiency machining process and its simulation

Madiha binti Zahari was born in Melaka, Malaysia. She received the bachelor's degree in electrical& Electronic Engineering from University Technology of Petronas in 2006 and Master of Engineering in Industrial Electronic and Control from University of Malaya. She was Process Engineer at Infineon Technologies (M) Sdn Bhd had responsible in wire bonding process. She is currently work as a Lecturer at Universiti Teknikal Malaysia Melaka

**Nurliyana Abd Mutalib** was born in Melaka, Malaysia. She received the bachelor's degree in electrical engineering from Universiti Tun Hussein Onn, Johor, Malaysia in 2006 and Master of Science in Microelectronics from Universiti Kebangsaan Malaysia. She was a Product Engineer in Freescale Semiconductor where she works on product improvement. She is currently work as Lecturer in UTeM and doing research under Micro and Nano Electronics (MINE).

**Siti Halma Johari** was born in Perlis, Malaysia. She received the bachelor's degree in Electronic Engineering (Industrial Electronics) from Universiti Teknikal Malaysia Melaka (UTeM) in 2005 and Master of Engineering in Control & Automation from University Of Malaya. She was a test engineer in Venture Electronic Services where she works on 1<sup>st</sup> level failure analysis and root cause investigation. From 2010 to 2014, she had been a teaching engineer and currently she work as lecture in UTeM and doing research under Photonics Engineering (PERG).

**Suziana Ahmad** was graduated in bachelor's degree of Electrical Engineering from Universiti Teknologi Malaysia in 2005. Then, she obtained her master's degree in industrial Electronic & Control from University of Malaya, Kuala Lumpur in 2014. She had experienced as R&D Electrical Engineer at Panasonic System Networks (M) Sdn. Bhd. for almost 5 years. In 2010, she continued her career as Teaching Engineer in Universiti Teknikal Malaysia Melaka and currently she is working as Lecturer in the same university.

Nuzaimah Mustafa hold Master of Science and bachelor's degree in Materials Engineering from Universiti Sains Malaysia. She has 9 years experienced in industry prior joining academic field as a lecturer in Universiti Teknikal Malaysia in 2011. Her publications includes United States Patent, US8709573B titled "Polymer Bonded Fibrous Coating on Dipped Rubber Articles Skin Contacting External Surface, Proceedings of Engineering Technology International Conference (ETIC 2015) titled "Engineering Technology Apprentice Program: A Case Study of Engineering Technology Faculty at UTeM", Proceedings of the 5<sup>th</sup> Postgraduate Seminar on Natural Fiber Composites titled "Incorporation of waste rubber into different matrices: A review", IOP Conference Series: Materials and Science Engineering titled "Recycling of Waste Rubber as Fillers: A review". She is currently conducting research of a polymer composite that utilizing rubber waste as its fillers.