# PAOD: a predictive approach for optimization of design in FinFET/SRAM

# Girish H<sup>1</sup>, Shashikumar D. R.<sup>2</sup>

<sup>1</sup>J C Bose Centre for Research & Development, Department of ECE, Cambridge Institute of Technology, K.R. Puram, Bangalore, India

<sup>2</sup>Department of Computer science Engineering, Cambridge Institute of Technology, K.R.Puram, Bangalore, India

#### **Article Info**

Article history:

# ABSTRACT

Received Apr 30, 2018 Revised Oct 12, 2018 Accepted Dec 8, 2018

#### Keywords:

Design structure FinFET Memory units Optimization Static RAM Yield The evolutions in the modern memory units are comeup with FinFET/SRAM which can be utilized over high scaled computing units and in other devices. Some of the recent systems were surveyed through which it is known that existing systems lags with improving the performance and optimization of FinFET/SRAM design. Thus, the paper introduces an optimized model based on Search Optimization mechanism that uses Predictive Approach to optimize the design structure of FinFET/SRAM (PAOD). Using this can achieve significant fault tolerance under dynamic cumpting devices and applications. The model uses mathematical methodology which helps to attain less computational time and significant output even at more simulation iteration. This POAD is cost effective as it provides better convergence of FinFET/SRAM design than recursive design.

Copyright © 2019 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

Girish H, J C Bose Centre for Research & Development, Department of ECE, Cambridge Institute of Technology, K.R. Puram, Bangalore, India. Email: hgirishphd@gmail.com

#### 1. INTRODUCTION

The use of miniature circuits in veriety of electronic and electrical device is rapily growing and hence concern towards memory utilization of SRAM [1]. The SRAM provides simple operation, accessibility and high speed process but its size and cost are the concerning issues [2], [3]. The cost of SRAM usage is greater than DRAM as it occupies more space than DRAM. Hence, the transistor design of FinFET is more studied for SRAM [4]. However, FinFET/SRAM also exhibits area, stability, output, access time, power consumption, etc issues [5], [6]. Other modeling like double gated, back gated design, designs with dynamic feedback were discussed in recent past for FinFET/SRAM design [7], [8]. It is observed that most of the design methodologies were hardware-based approach as well as prototyping but there exist some open-end problems and are not solved i) predictive design model of FinFET/SRAM is introduced to offer better performance with accuracy, ii) existing studies have narrowed scale of implementation error which doesn't seem to offer fault tolerance to the SRAM design, iii) least works were carried out to jointly study the impact of design on output, energy, and memory units response. Thus, a better design optimization is not found from the literature which motivates the research community to have futuristic design optimization of FinFET/SRAM. This manuscript presents a predictive Approach for Optimization of Design in FinFET/SRAM. The manuscript is categorized as: Section 2 presents existing research work and problem identification in Section 3. Proposed methodology is given in Section 4 and elaborated discussion of algorithm implementation in Section 5. The accomplished outcomes were analyzed with comparative analysisis represented in Section 6 followed by conclusion in Section 7.

# 1.1. Background

The existing system on SRAM is presented in (Girish and Shashikumar [9]) is presented and identified certain set of problems of cost optimization that was addressed in most recent implementation (Girish and Shashikumar [10]). This section discusses approaches towards enhancing performance of FinFET/SRAM. The work of Bhattacharya and Jha [11] addressed the problem of stabilization of its reading operation using monolithic integration approach. Study toward identification of errors in SRAM by Fang and Oates [12]. Chen et al. [13] have introduced a technique for facilitating an effective writing operation for reducing the supply voltage. Yang et al. [14] addressed the problem associated with near-threshold based operation improving the reading performance. Karl et al. [15] has developed a prototype design of SRAM emphasizing on collapsing voltage for minimizing energy consumption during write operation. Zhang et al. [16] have performed optimization using dopant over their prototype of SRAM targeting as scaling the voltage factor. Kulkarni et al. [17] have adopted an amplification technique for enhance sensing performance in FinFET. Hu et al. [18] have presented SRAM design with better improvement over noise for improved performance of reading and writing operation. Bhattacharya and Jha [19] have presented a synthesis-based approach for accelerating the process of extracting the capacitance factor for a given layout arrays of SRAM. The technique also introduces an exclusive partitioning process for better efficiency. Song et al. [20] have presented a scheme for addressing the power issue in 128 mb of SRAM focusing on multiple density factors. Mishra and Mahapatra [21] have carried out a simulation-based approach for investigating the stability problems associate with SRAM. This work is reported to offer fault tolerance operation however their approach was limited to only normal operating conditions of circuits. Asenov et al. [22] have presented a unique approach of design optimization considering variability factor in the simulation study. The work carried out by Joshi et al. [23] has investigated variability of devices with respect to the SRAM using statistical approach. Mounica and Ganesh [24] have illustrated about new NVSRAM circuit that generates superior "instant-on operation" related to previous methods used in SRAM's. Riyadi et al. [25] have demonstrated the influence of gate material and process on subthreshold performance of junctionless FET, by comparing four sets of gate properties and process methods. All the above existing approaches do not address the design optimization problem of FinFET/SRAM and hence offers a broader scope of carrying out a research work.

#### **1.2.** The problem

After reviewing the existing approaches towards FinFET/SRAM design, good amount of research using hardware platform were found but none of these works have given optimal throughput and improved performance. Hence, existing approaches couldn't offer fault tolerance as they were no much standard computational model with an extensive analysis to prove it. Moreover, the memory units and their respective communication with other connected memory units have not been investigated in past ith respect to memory and power that is significant degraded in the upcoming design of chip multiprocessor. Therefore, the problems statement is "design a system which can balance multiple aspects like power consumption, increased output, and faster processing."

#### 2. PROPOSED METHODOLOGY

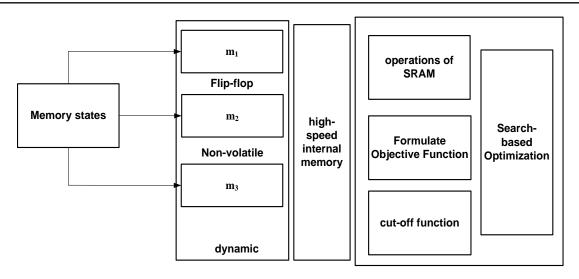

The proposed system a predictive Approach for Optimization of Design in FinFET/SRAM to enhance the throughput performance. The following Figure 1 gives proposed system architecture.

The proposed system introduces three different functionalities of FinFET/SRAM which when combined with internal memory should offer maximum throughput without any dependencies of increasing resources. A novel mechanism of search-based optimization scheme is applied that considers various operations of SRAM, formulates an objective function, whose process is controlled by a novel cut-off function in order to achieve convergence. The next section briefs about algorithm implementation.

Figure 1. Implemented system scheme

# 3. ALGORITHM DESIGN

For a memory unit to be fault tolerant, it is necessary to ensure that it can cater up all the situation of resource utilization and querying process. It is also necessary to ensure how each memory units communicates with each other in order to accomplish the processing task. Therefore, the formulation of the proposed system is carried out for multiple states of memory corresponding to FinFET/SRAM. The proposed algorithm introduces a novel search-optimization-based predictive approach where the input to the algorithm are m1, m2, m3 (different memory),  $\alpha$  (operations of SRAM),  $\gamma$  (high speed memory (internal)),  $\sigma$  (memory units),  $\tau$  (cut-off function), pdef (defined parameter) and final outcome is accomplishment of converging point. The incorporated steps of the algorithm are:

Algorithm for design optimization of FinFET SRAM Input:  $m_1$ ,  $m_2$ ,  $m_3$ ,  $\alpha$ ,  $\gamma$ ,  $\sigma$ ,  $\tau$ ,  $p_{def}$ Output:converging point Start 1. *init*  $\rightarrow$  m<sub>1</sub>, m<sub>2</sub>, m<sub>3</sub> 2. Set  $f_{obj}(x) \to \sum_{i=1}^{5} \alpha$ 3. form Matrix  $\beta = [m_{\text{prime}}, M_{\text{onchip}}]$ 4. arrange  $\beta = \gamma(m_1, m_2, m_3)$  in  $\sigma$ 5. compute  $\tau = abs \{H\}$ 6. While  $\tau$  is not achieved do 7. Forp=0 to  $\mu$ 8. randSelect( $p_{def}$ ) from  $\mu$ 9.  $r_{adap} \rightarrow g(\tau)$ 10. End 11. Assess all outcomes and shortlist best 12. End 13. Convergence achieved End

The algorithm focuses on coupling of SRAM memory states by considering high speed internal memory for speeding up the computation process. The variables m1, m2, and m3 correspond to higher capability of memory (Line-1). The algorithm also formulates an objective function to ensure design optimization. The proposed algorithm formulates an objective function "fobj(x)" which has dependency of 5 parameters of operations of SRAM i.e.  $\alpha 1$ ,  $\alpha 2$ ,  $\alpha 3$ ,  $\alpha 4$ , and  $\alpha 5$  corresponds to i) reading operation in local memory along with its cost, ii) writing operation in local memory with its cost, iii) reading operation of remote memory along with its cost, iv)writing operation of remote memory along with its cost, iv)writing operation of remote memory along with its cost, iv)writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, iv) writing operation of remote memory along with its cost, and v) cost of making the data go mobile from one to another memory segment (Line-2). The matrix  $\beta$  is created which maintains two forms of memory i.e. prime memory (Mprime) and on chip memory (Monchip). The next step

963

defines a function  $\gamma$  (high speed memory) where the memory elements are going to be structured for direct accessibility when queried for allocation (Line-4). This step impacts on positive energy saving and balanced allocation of necessary resources. The algorithm than initiates begin its search optimization for obtaining better convergence point of design. For this, we apply a novel formulation of a cut-off function  $\tau$  that we choose to compute instead of initializing like in majority of studies in existing system. The computation of the cut-off function is carried out by computing a matrix H which depends on cumulative state of memory and cost function (Line-5). The complete evaluation is also dependent on cardinality of data items as well as cost of data as well. Line-6 to Line-12 corresponds to proposed search optimization scheme with an intention to obtain better convergence point of design of SRAM. The initial step in this search-based optimization is to perform random selection of population, where population is a set of all best possible outcomes of resource allocation policies of FinFET/ SRAM. The proposed system will apply a greedy approach in order to perform random selection of populationµ (Line-8). The next step is to apply a function g on cut-off function (Line-9), which corresponds to replicate behaviour with adaptive approach radap. This process is enhancement on the prior population extraction where it offers formulating more elite outcome from a set of one of more elite population. The computation of the function  $g(\tau)$  mainly depends on maximum value  $\tau$  max, best value  $\tau$  best, and average value of cut-off function  $\tau$  avg and is empirically represented as,

$$g(\tau) = c.\frac{\tau^p}{\tau^q} \tag{1}$$

Where the notation  $\tau p$  and  $\tau q$  corresponds to ( $\tau max$ -  $\tau best$ ) and ( $\tau max$ -  $\tau avg$ ) respectively. The variable c represents system matrix whose values depends on final application to be designed and hence could be configured likewise. The prime idea of this search optimization is to assess the presence of sufficient resource for allocation of particular memory units in FinFET/SRAM. It also has the capability to assess its adjacent cores of memory units and easily localize certain units. Such approaches are not seen in any existing approach for design enhancement of SRAM. The final step of search optimization includes resisting of the accomplishing the convergence point. We define convergence point as an instance of an outcome where minimal resource is used to obtained better yield of SRAM that is more capable of making it fault tolerant. Therefore, the final step of proposed algorithm is to performing sorting and to check for the best values of the outcome. The process is continued until and unless all the populations  $\mu$  are checked (Line-11 and Line-13). An interesting fact to see for is the process of swapping the memory unit with each other in order to cater up the dynamic job requirements. This process results in building more capability to the FinFET / SRAM for exhibiting better convergence performance with less inclusion of memory parameters. Hence, this proposed optimization technique will also ensure better energy conservation scheme as well as it also has the capability to minimize and control of leakage power. At the same time, the proposed algorithm encourages progressive steps and not iterative steps, for which reason computational burden is kept within a specific limit. The next section outlines the results being obtained.

#### 4. **RESULTS DISCUSSION**

The MATLAB is used for simulation over 6-bit machine of windows platform. A hypothetical task is generated to assess the memory factor with respect to throughput and response time. The test platform uses core i3 process of 2GHz frequency. The baseline memory states m1, m2, and m3 are configured with multiple energies of 0.2nJ-20nJ, 0.5ns-20ns and 2mW-100mW for access operation, delay and leakage power respectively. The system outcomes using Search Optimization (SO) is compared with Particle Swarm Optimization (PSO).

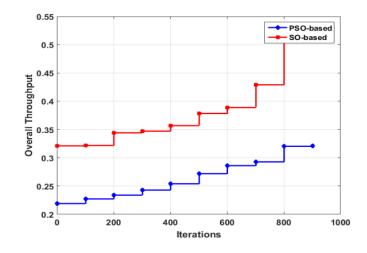

Figure 2 highlights that proposed system of SO offers better throughput performance in contrast to PSO based approach. The prime reason for this trend is – PSO based design optimization scheme offers iterative process to obtain the elite outcome of convergence. This causes increase in latency owing to excessive read-write operation resulting in maximum resource allocation. Hence, PSO based schemes offers fault tolerance for only lesser iteration. In the meanwhile, proposed SO-based scheme offers a progressive exploration process where the all the cumulative outcomes are already defined and process of optimization narrows down the search process using a cut-off function and hence makes the process much progressive and less iterative. Normally, such optimization process is not witness in existing FinFET/SRAM design in any of the existing system and hence our proposed system can be said to offer better balance between the energy being depleted dring read-write operation.

Figure 2. Comparative result of throughput

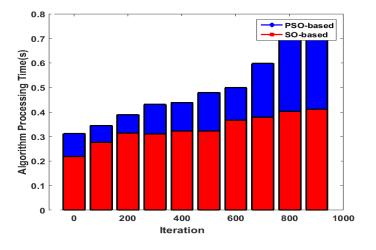

Figure 3. Comparative result of response time

A closer look into the proposed technique shows that it offers significant reduction of the write operation up to 35% and minimizes energy consumption to 20% approximately. Owing to adoption of randomized process of initiating a search, proposed algorithm performs faster operation which contributes to faster algorithm execution time. The second reason for faster response time is that proposed algorithm performs parallel search process of obtaining elite outcome of convergence point. This cut downs the computational time to 50% and is quite useful for handling massive and dynamic task. At the same time, greedy mechanism further simplifies the process of initiating and managing the search depending on the best value of the cut-off function that consistently updates it. The computational complexity in Figure 3 of the proposed system is therefore very less and it has nearly uniform trend, which makes the performance quite predictive for the proposed system. The outcome of graphical trend therefore exhibits that proposed system offers better throughput performance measured with respect to probability that could suit well to any form of applications using FinFET/SRAM with less energy consumption, more yield, and faster computational time. It is best suitable for upcoming designs of registers with high speed operation, sophisticated smart phones with advanced mobile networks, buffer management in n-based routers, etc.

# 5. CONCLUSION

The proposed system introduces three different roles of SRAM in the form of memory units aiming to to minimize the energy depletion and other issues concerning with the latency. The proposed technique gives a an optimized model based on Search Optimization mechanism that uses Predictive Approach to optimize the design structure of FinFET/SRAM (PAOD). The implementation of system is a computational

model that suits well with any computational environment. The study outcome shows that proposed system offers better response and higher throughput.

#### REFERENCES

- [1] B. Wicht, "Current Sense Amplifiers for Embedded SRAM in High-Performance System-on-a-Chip Designs," *Springer Science & Business Media*, 2013.

- [2] M. Alioto, "Enabling the Internet of Things: From Integrated Circuits to Integrated Systems," Springer, 2017

- [3] G. Sun, "Exploring Memory Hierarchy Design with Emerging Memory Technologies," Springer Science & Business Media, 2013.

- [4] S. Dasgupta, B. K. Kaushik, P. Kumar Pal, "Spacer Engineered FinFET Architectures: High-Performance Digital Circuit Applications," *CRC Press*, 2017.

- [5] R. Reis, Y. Cao, G. Wirth, "Circuit Design for Reliability," Springer, 2014.

- [6] G. Gildenblat, "Compact Modeling: Principles, Techniques and Applications," *Springer Science & Business Media*, 2010.

- [7] Y. S. Chauhan, D. D. Lu, V. Sriramkumar, S. Khandelwal, "FinFET Modeling for IC Simulation and Design: Using the BSIM-CMG Standard", *Academic Press*, 2015.

- [8] N. H.E. Weste, D. Harris, "CMOS VLSI Design: A circuits and systems perspective", *Pearson Education India*, 2015.

- H. Girish, Shashikumar D.R., "Insights of Performance Enhancement Techniques on FinFET-based SRAM cells," *Communications on Applied Electronics (CAE), Foundation of Computer Science*, vol. 5, no. 6, 2016.

- [10] H. Girish, D. R. Shashikumar, "Cost-Effective Computational Modeling of Fault Tolerant Optimization of FinFET-Based SRAM Cells," Springer- Computer Science On-line Conference, pp.1-12, 2017.

- [11] D. Bhattacharya and N. K. Jha, "Ultra-High Density Monolithic 3-D FinFET SRAM with Enhanced Read Stability," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 8, pp. 1176-1187, Aug. 2016.

- [12] Y. P. Fang and A. S. Oates, "Characterization of Single Bit and Multiple Cell Soft Error Events in Planar and FinFET SRAMs," in *IEEE Transactions on Device and Materials Reliability*, vol. 16, no. 2, pp. 132-137, June 2016.

- [13] Y. H. Chen *et al.*, "A 16 nm 128 Mb SRAM in High- \$kappa\$ Metal-Gate FinFET Technology With Write-Assist Circuitry for Low-VMIN Applications," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 1, pp. 170-177, Jan. 2015.

- [14] Y. Yang, J. Park, S. C. Song, J. Wang, G. Yeap and S. O. Jung, "Single-Ended 9T SRAM Cell for Near-Threshold Voltage Operation With Enhanced Read Performance in 22-nm FinFET Technology," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 11, pp. 2748-2752, Nov. 2015.

- [15] E. Karl et al., "A 0.6 V, 1.5 GHz 84 Mb SRAM in 14 nm FinFET CMOS Technology With Capacitive Charge-Sharing Write Assist Circuitry," in *IEEE Journal of Solid-State Circuits*, vol. 51, no. 1, pp. 222-229, Jan. 2016.

- [16] X. Zhang, D. Connelly, H. Takeuchi, M. Hytha, R. J. Mears and T. J. K. Liu, "Comparison of SOI Versus Bulk FinFET Technologies for 6T-SRAM Voltage Scaling at the 7-/8-nm Node," in *IEEE Transactions on Electron Devices*, vol. 64, no. 1, pp. 329-332, Jan. 2017.

- [17] J. P. Kulkarni et al., "5.6 Mb/mm \$^{2}\$ 1R1W 8T SRAM Arrays Operating Down to 560 mV Utilizing Small-Signal Sensing With Charge Shared Bitline and Asymmetric Sense Amplifier in 14 nm FinFET CMOS Technology," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 1, pp. 229-239, Jan. 2017.

- [18] V. P. H. Hu, M. L. Fan, P. Su and C. T. Chuang, "Analysis of GeOI FinFET 6T SRAM Cells With Variation-Tolerant WLUD Read-Assist and TVC Write-Assist," in *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1710-1715, June 2015.

- [19] D. Bhattacharya and N. K. Jha, "TCAD-Assisted Capacitance Extraction of FinFET SRAM and Logic Arrays," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 1, pp. 329-333, Jan. 2016.

- [20] T. Song *et al.*, "A 10 nm FinFET 128 Mb SRAM With Assist Adjustment System for Power, Performance, and Area Optimization," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 1, pp. 240-249, Jan. 2017.

- [21] S. Mishra and S. Mahapatra, "On the Impact of Time-Zero Variability, Variable NBTI, and Stochastic TDDB on SRAM Cells," in *IEEE Transactions on Electron Devices*, vol. 63, no. 7, pp. 2764-2770, July 2016.

- [22] A. Asenov *et al.*, "Variability Aware Simulation Based Design- Technology Cooptimization (DTCO) Flow in 14 nm FinFET/SRAM Cooptimization," in *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1682-1690, June 2015.

- [23] R. Joshi *et al.*, "A Universal Hardware-Driven PVT and Layout-Aware Predictive Failure Analytics for SRAM," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 3, pp. 968-978, March 2016.

- [24] J. Mounica, G.V. Ganesh, "Design of a Nonvolatile 8T1R SRAM Cell for Instant-On Operation," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 6, no. 3, pp. 1183-1189, 2016.

- [25] Riyadi, Munawar A., Irawan D. Sukawati, Teguh Prakoso, and Darjat Darjat, "Influence of Gate Material and Process on Junctionless FET Subthreshold Performance", *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 6, no. 2 (2016): 895-900.

# **BIOGRAPHIES OF AUTHORS**

**Girish H**, He received his B.E in ECE from Kuvempu University, Karnataka, India & M Tech from Visvesvaraya Technological University (VTU), Belgaum, India. He is pursuing PhD in VTU. His area of interest is VLSI and Embedded System. He is currently working as Associate Professor in Department of Electronics and Communication, Cambridge Institute of technology, Bangalore-36, India.

**Dr. Shashikumar D. R**, He received his B.E in ECE from Mysore University (MU), Karnataka, India & M. E from Bangalore University (BU), Karnataka, India. He received his PhD degree from Fakir Mohan (FM) University, Balasore, Orissa. His area of interest is VLSI, image Processing. He is currently working as Professor and Head of the Department of Computer Science Engineering, Cambridge Institute of technology, Bangalore-36, India. He has published more than 20 International journals and 20 National journals. Currently, he is guiding 6 PhD scholars.