# A Survey: Space Vector PWM (SVPWM) in 3φ Voltage Source Inverter (VSI)

**Shalini Vashishtha<sup>1</sup>, K.R. Rekha<sup>2</sup>** <sup>1</sup>Visvesvaraya Technological University, Belagavi, India <sup>2</sup>Dept of ECE, SJBIT, Bangalore, India

### Article Info

### Article history:

Received Feb 23, 2017 Revised Jun 19, 2017 Accepted Oct 3, 2017

#### Keyword:

Analog circuits Digital circuits FPGA PWM Sinusoidal PWM SVPWM Total harmonic distortion (THD) VSI

## ABSTRACT

Since last decades, the pulse width modulation (PWM) techniques have been an intensive research subject. Also, different kinds of methodologies have been presented on inverter switching losses, inverter output current/ voltage total harmonic distortion (THD), inverter maximum output of DC bus voltage. The Sinusoidal PWM is generally used to control the inverter output voltage and it helps to maintains drive performance. The recent years have seen digital modulation mechanisms based on theory of space vector i.e. Space vector PWM (SVPWM). The SVPWM mechanism offers the enhanced amplitude modulation indexes (MI) than sinusoidal PWM along with the reduction in the harmonics of inverter output voltage and reduced communication losses. Currently, the digital control mechanisms have got more attention than the analog counterparts, as the performance and reliability of microprocessors has increased. Most of the SVPWM mechanisms are performed by using the analog or digital circuits like microcontrollers and DSPs. From the recent study, analysis gives that use of Field Programmable Gate Arrays (FPGA) can offer more efficient and faster solutions. This paper discusses the numerous existing research aspects of FPGA realization for voltage source inverter (VSI) along with the future line of research.

> Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

### Corresponding Author:

Shalini Vashishtha, Visvesvaraya Technological University, Belagavi, India. Email:- shaliniv.vtu@gmail.com

## 1. INTRODUCTION

The concepts of PWM are turning out to be increasingly prevalent in today's motor drives. In the inverters, PWM makes it conceivable to control both the frequency and magnitude of the current and voltage connected to a motor. Along these lines, PWM for motor drives offers better efficiency and higher performance contrasted with fixed frequency motor drives. PWM systems have been the subject of serious research amid the most recent couple of decades. The PWM techniques have been the intensive research subject. Also, different kinds of methodologies have been presented on inverter switching losses, inverter output current/ voltage THD, inverter maximum output voltage of DC bus voltage [1].

The sinusoidal PWM is utilized to control the output current/voltage of the inverter and keeps up a better performance of the drive in the whole operational range between 0-78percent of the value that would be come to by square operation. In the event that the MIs surpass this value, straight relationship amongst MI and output voltage is not kept up, and the over modulation techniques are required. As of late, a characteristically advanced modulation system known as SVPWM which depends on space vector hypothesis [2]. It has been accounted for that SVPWM mechanisms offers better performance over different methods regarding torque ripple, better DC link utilization, lower THD, switching loss and easier digital system

implementation [3]. The SVPWM systems have been rapidly used, as it allows reducing commutation losses and obtaining higher amplitude MIs if compared with Sinusoidal PWM techniques [4]. Currently, the digital control mechanisms have got more attention than the analog counterparts, as the increased performance and reliability of microprocessors [5]. Most of the SVPWM mechanisms are performed by using the analog or digital circuits like microcontrollers and DSPs [6], [7].

The utilization of FPGA gives more faster and efficient solution, as it can complete parallel processing by hardware mode which involves nothing of CPU, the framework can get a fast level [8]. The field programmable capacity of FPGA's, and the adaptable modification of dead time, the adaptable modification of dead time exchanging frequency makes it reasonable to drive different switching devices in down to earth applications [9].

The SVPWM includes complex computations. In the work of [10] and [11] digital signal processors was utilized to play out the number juggling counts. For this situation, least two processors are needed for implementation of the technique. The every count of processors are done offline and put away in memory. Despite the fact that memory space is vast contrasted with past techniques, it takes least getting to time. It doesn't influence the speed of operation. Memory is additionally modified in FPGA itself and so no need of outside memory. Moreover, there are many preferences because of the fast outline process and reprogrammable capacities for FPGA [12]. The FPGA empowers to deliver model pro type logic in a less period. It is conceivable to make, actualize, and perform verification of the new design.

This paper is organized as Section 2 mentions conceptual description of voltage source inverter (VSI),  $3\phi$  VSI, space vector PWM (SVPWM), significance of SVPWM, Xilinx FPGA flow, etc. In section 3 existing researches are discussed with their significances. Section 4 states the research gap while Section 5 provides the future line of research in SVPWM. Section 6 gives the conclusion.

### 2. VOLTAGE SOURCE INVERTER (VSI)

The smallest circuit which used to convert direct-current (DC)-to-alternating-current (AC) is known as the inverter. The battery power is converted into AC power or main voltages and this power used for different electronic appliances such as mobiles, television, computer, etc. The main functionality of inverter is to convert DC to AC (DC-AC), and a step-up transformer is implemented to generate main voltages from AC.

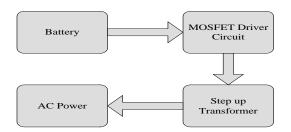

Figure 1. Inverter Block Diagram

In above inverter block diagram, battery supply is fed to MOSFET driver in which DC to AC conversion may take place, and the resulting AC is fed to step up transformer to get original voltage. Inverters can be classified as:

- a. If the DC voltage is constant and this inverter is known as Voltage Source/ voltage fed Inverter.

- b. If input current is kept constant and is known as Current Source or Current Fed.

#### 2.1. Voltage Source Inverter (VSI)

- a. This takes fixed voltage as input from a device and gives AC supply with variable-frequency. The VSI are classified as Square-wave Inverters, 1φ Inverters with Voltage Cancellation, Pulse-width Modulated (PWM) Inverters.

- b. Square-wave inverters (SWI): In this input is connected to controlled dc voltage to control the output AC voltage magnitude. The inverter only controls the output frequency with controlled input voltage magnitude. The output voltage has square wave type.

- c. Pulse-width modulation (PWM) inverters: This takes constant dc voltage as input, where dioderectifiers are utilized for line voltage rectification and inverter should control the frequency and magnitude of the AC output voltages. There are different methods to perform the PWM in an inverter to shape output AC voltages to make a sine wave.

- d. 1φ Inverters: In this voltage, cancellation is considered as constant dc source and an output squarewave. The output controls both frequency and magnitude but does not use PWM.

- e. Switch-mode dc-to-ac (SM dc-ac) inverters: These are utilized for Uninterrupted power supply (UPS) in which a sinusoidal ac output is needed to be provided with controlled frequency and magnitude.

#### 2.2. 3 VSI

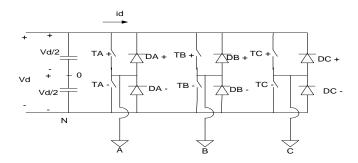

The  $3\varphi$  VSI creates less harmonic distortion at output voltage used in the phase to phase AC load. A  $3\varphi$  VSI circuit model is shown in Figure 2, along with six different switch ((TC+ and TC-, TB+ and TB-, or TA+ and TA-)). These switches in  $3\varphi$  VSI can't be switched on all the while at grounds this may give a short circuit over the voltage supply of dc link. Thus, to move from undefined states in the VSI, the switches of any inverter leg can't be switched off all the while as this will bring about voltages that will rely on the separate polarity of line current.

Figure 2. Circuit of 3 VSI

Numerous applications that require an inverter utilizes  $3\phi$  control. Two main cases are AC-motor drive and UPS [3]. This can be obtained by three legs, one of every phase. The inverter output voltage can be balanced. The most cases PWM control utilized within an inverter. The upsides of PWM techniques are specified as:

a. The control of output voltage with PWM can be obtained with fewer components.

b. With the controlling of the output voltage, lower order harmonics can be minimized or erased. PWM inverters are more utilized for industrial applications [4].

#### 2.3. Space-Vector-Pulse-Width-Modulation (SVPWM)

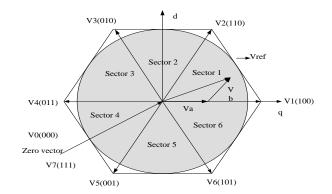

switching. The inverter switching gives eight output-vectors with six being active  $V_1, V_2, V_3, V_4, V_5$  and  $V_6$

or non-zero and two zero-vectors  $V_0, V_7$ . The converted diagram of voltage vectors into two axes represented in Figure 2. The non-zero vectors tips are cornered to form a regular hexagon consisting of two zero vectors joining at the origin.

Space vector theory represents the  $3\varphi$  voltages as voltage space vector rotates in the (d-q) plane. The vector magnitude is related to phase voltages magnitude and the time to cover one revolution is the period of fundamental phase voltages. The inverter power switches are used to obtain voltage vectors according to different switching positions. These voltage vectors represent active vectors that subdivide the plane into equal sectors, and non-active vectors, sometimes call zero vector at an origin. The desired three-phase sinusoidal output voltages correspond to a circle in the (d-q) given in Figure 3.

Figure 3. Voltage-vectors in d-q plane

The output line and phase voltages for each space vector are shown in Table 1. The  $2\phi$  components can be calculated by using the Equation (1).

| Table 1. 3\u03c6 Inverter Output Voltages |           |                 |              |  |  |  |  |  |  |

|-------------------------------------------|-----------|-----------------|--------------|--|--|--|--|--|--|

| ltage                                     | Switching | Line to neutral | Line to Line |  |  |  |  |  |  |

| ctors                                     | vectors   | voltage         | Voltage      |  |  |  |  |  |  |

| Voltage<br>vectors    | Switching<br>vectors |   |   | Line to neutral<br>voltage |      |      | Line to Line<br>Voltage |    |    |

|-----------------------|----------------------|---|---|----------------------------|------|------|-------------------------|----|----|

| V <sub>0</sub>        | 0                    | 0 | 0 | 0                          | 0    | 0    | 0                       | 0  | 0  |

| V <sub>1</sub>        | 1                    | 0 | 0 | 2/3                        | -1/3 | -1/3 | 1                       | 0  | -1 |

| <b>V</b> <sub>2</sub> | 1                    | 1 | 0 | 1/3                        | 1/3  | -2/3 | 0                       | 1  | -1 |

| V3                    | 0                    | 1 | 0 | -1/3                       | 2/3  | -1/3 | -1                      | 1  | 0  |

| V4                    | 0                    | 1 | 1 | -2/3                       | 1/3  | 1/3  | -1                      | 0  | 1  |

| V5                    | 0                    | 0 | 1 | -1/3                       | -1/3 | 2/3  | 0                       | -1 | 1  |

| V <sub>6</sub>        | 1                    | 0 | 1 | 1/3                        | -2/3 | 1/3  | 1                       | -1 | 0  |

| V <sub>7</sub>        | 1                    | 1 | 1 | 0                          | 0    | 0    | 0                       | 0  | 0  |

### 2.4. Role of FPGA over SVPWM

Recently some control systems have been considered to deign using FPGA; FPGA integrated circuit. Implementation of SVPWM by using FPGA has been studied by a few researchers; a novel space SVPWM algorithm for multiplevel multiplase voltage source converters is presented in [1]. In work of [3], an efficient SVPWM algorithm is discussed to reduce the resource usage, which evolves reduction in computational overheads and also removes the high sampling time issues for real-time applications.

#### 2.5. Xilinx FPGA Design flow

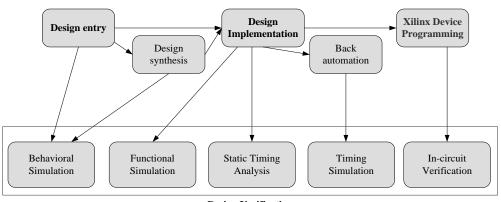

The FPGA design methodologies include VHDL or Verilog languages, synthesis, map, and place and route scheme. The considerations are pin-pin delays, pipelining and logic levels, and floor planning, etc. FPGAs are now posses logic capacity and sufficient performance to implement a number of DSP algorithms effectively. This is achieved with exploiting parallelism and also by mapping mechanism like distributed arithmetic. At present, a single FPGA platform can replace for multiple applications, including controllers, filters, and interfaces. Efficient FPGA circuits obtained by design techniques, which traditionally relies on the processor hardware together with smart compiler technology. The block diagram for FPGA design flow is as shown in Figure 4. The FPGA design flow is consists of the following stages.

Design Entry - In this stage of the hardware description language (HDL), design flow is used for texta. based entry, a schematic editor, or both is used to create the design.

- **D** 15

- b. Design Implementation- Using the design in Xilinx architecture, logic design file format is generated at a stage of design entry is converted to a physical file format. This physical information is existed at native circuit description (NCD) file to use FPGAs. Then a bit stream file is created.

- c. Verification of Design- By using Xilinx XChecker cable, gate level simulator or JTAG cable, to ensure that the design meets the timing requirements and functions properly.

Design Verification

Figure 4. Xilinx flow Design

### 3. EXISTING RESEARCH

The existing researches in the field of VSI are surveyed and discussed in this section. The survey is categorized as realization with the FPGA and without FPGA, where the researches performed in both the techniques are discussed.

## 3.1. Researches on SVPWM without FPGA

The works of Shao et al. [13] have given a generalized concept of Discontinuous SVPWM (DSVPWM) for  $3\varphi$  VSI. The methods consist of six sectors like DSVPWMP, DSVPWMPN0, DSVPWMNN, DSVPWMPN1, DSVPWMPN2, and DSVPWMPN3 and are re-divided into twelve 1's based on local over modulation and SVPWM method. The principle of DSVPWMx is developed, and the traditional discontinuous pulse width modulation (DPWM) strategies are studied on the basis of THD and switching loss. The results state DSVPWMx strategies are feasible.

In Badran et al. [14] Digital Implementation of SVPWM Technique Using 8-bit Microcontroller is presented. Authors study is meant to develop a novel inverter design. In this, a 8-bit microcontroller is utilized to generate SVPWM signal needed for triggering the MOSFET bridge gates of the inverter. Here the inverter composed of a low-pass LC-filter to generate the output of sine waveform. In this microcontroller was used for implementation of SVPWM algorithm. Six pins of Port B of the microcontroller were used to send the output pulses. The software that was used for PIC microcontroller programming was MikroC compiler, while WinPIC800. The experimental outcome represents the effectiveness of the system to generate a  $3\varphi$  sine wave at the better frequency.

The work of Boudouda et al. [15] provided combined random SVPWM using induction motor for variable speed drive. This research work focused on implementing Random space vector modulation. The analysis of the output voltage based on the PSD of random signals clearly shows the obtained spreading of the PSD and the important reduction of the peaks, compared to other simple and dual random techniques and to the conventional deterministic technique, which is the sought EMC advantage. The author method provides the good PSD performance.

Author Choudhari et al. [16] have given the SVPWM on DSP Platform for Utility Grid Synchronizable Tieline Converter between AC-bus and DC-bus of aMicrogrid. The study aims to develop Space vector pulse width modulation on DSP. In this, the PWM modules architecture based on DSP is explained. The presented inverter is simulated using existing microgrid architecture scenarios are discussed.

The design and implementation of SVPWM inverter based on cost effective microcontroller were presented in Gaballah [17]. The study was intended to develop a modulation technique with less THD, wider linear modulation range, and fewer switching losses. The practical outcomes give that the better performance at faster computation time along with less complexity in software implementation is achieved with presented SVPWM than traditional SVPWM.

The combined work of Kassas and Ahmed [18] states the simulation and implementation of SVPWM using the look-up table. This work is meant to use Loop up the table for designing SVPWM. From this SVPWM a Simulink model was introduced to verify the lookup table scheme (LTS) viability and its practical assumptions. The performance was compared among practical and simulated LTS results. The LTS shows the nearest THD to simulation results.

The combined work was performed by Kumar and Singh [19] states the DSP Based IFO Control of HEV fed through Impedance Source Inverter. The intention of the work is to achieve the good performances of speed control of the electric vehicle (induction motor) fed Z-source inverter using DSP controller. This method employs  $3\varphi$  six sinusoidal reference signals, and one triangular wave of high frequency as carrier signals. In this project, impedance source-inverter with IFOC system will be designed with a single DSP controller using the TMS320F28335, a new kind of DSP chip of Texas Instrument (TI). The reason to use this one is that the integrated and flexible features in the device meet the requirements we need for a control system. The hybrid indirect field oriented controlled induction motor drives speed control with is verified with simulation. The speed control on induction motor is controlled even input DC source voltage changes.

Author Kumar et al. [20] presented the digital control of SVPWM based on shunt active filter. The THD measured a show that using the proposed topology provides better compensation of harmonics and the implementation can be done by TMS320F28027 processor.

Mirazimi et al. [21] presented the SVPWM for Two-Phase Three-Leg Inverters. The study meant to develop a novel SVPWM. This proposed control scheme allows independent control of the magnitude and quadrature phase angle for two output phases. Thus, the presented two-phase inverter and its modulation scheme make the two-phase inverter commensurate with both balanced and unbalanced two-phase loads. Simulation results by using MATLAB/SIMULINK reconfirm the feasibility of the structure based on SVPWM method for the inverter.

Piao and Hung [22] presented a control strategy for balancing dc-link capacitor voltage in multilevel diode clamped VSI based on discontinuous SVPWM. The theoretical analysis and simulation results suggest that the proposed strategy is feasible.

Promkhun and Kinnares [23] have given Speed Control of an Asymmetrical Type Two-Phase Induction Motor Using DiscontinuousSpace Vector Pulse Width Modulation. The proposed DSVPWM can reduce switching losses of the motor side inverter. Single-phase full bridge switched-mode converter is used to improve power quality and allow regenerative power to grid. This system is simulated by MATLAB/Simulink. The results of the motor side show quick response and good performance for the twophase induction motor control in both steady and dynamic responses.

Sun et al. [24] have presented the  $3\varphi$  dual Buck Inverter based on unified PWMs. The work aims to design three-phase four leg inverter based on dual-buck power cell. The Efficiency measurement of PWMs is conducted, and the inverter achieves 98.8% of peak efficiency.

## 3.2. Research on VSI with FPGA

Author Castro et al. [25] have given the variable-clock-phase shifting based high-resolution FPGA Digital PWM. The current FPGA exhibit above feature thus allows small and introduces programmable delays between input and output clocks. The experimental outcome gives a 19.5ps time resolution using Virtex-5 FPGA.

The work of Orithi and Julian [26] have expressed the  $3\varphi$  VSI with FPGA-based multi-sampled SVPWM. The modulator and the inverter controller are used using an FPGA platform, and bandwidth is increased with respect to a digital signal processor (DSP) or with the microprocessor controller. This bandwidth results from low output voltage THD. The experimental results are represented by state space model of a VSI with an output LC filter.

Pan et al. [27] illustrated a shifted SVPWM mechanism for controlling the DC-Link Resonant Inverters FPGA Realization. The mechanism exhibit same effective vectors. A shifted SVPWM mechanism for dc-link inverters results show that the method is feasible for shifted SVPWM mechanism.

A concept to attain FPGA realization was performed by Rajendran et al. [28] using FPGA. In this FPGA is employed to realize PWM strategies and meets the high-switching-frequency and reconfigurable-structure issues for various applications. The realization and analysis of SVPWM were performed under variable-speed-control of ac motor drives by using Xilinx. The complete execution time of SVPWM direct torque controller achieved was 3.5µs.

Rohit et al. [29] an FPGA Implementation of SVPWM mechanism for  $3\varphi$  Induction Motor using a Fixed Point Realization. The design a high performance and low powered VHDL based SVPWM controller for  $3\varphi$  Induction Motor drive on FPGA. The SVPWM technique is an important PWM generation mechanism for  $3\varphi$  VSI to generate PWM signals to control different AC Motors. In this work the software part is implemented with proposed fixed point realization which increases the accuracy; also since there are

no subroutines, it reduces the total area on FPGA board. The density of the code is less, which reduces execution time and power consumption. The effectiveness of the method was analyzed with integer realization.

Rashidi and Sabahi [30] have expressed the high-Performance FPGA-Based Digital SVPWM (DSVPWM)  $3\varphi$  VSI. The study aims to design a high performance based low power DSVPWM controller using FPGA for  $3\varphi$  VSI. This method is proposed to accurate and high performance based DSVPWM technique of FPGA with fewer resources and minimum execution time. The authors DSVPWM algorithm was synthesized to implement over FPGA. In this controller's total power consumption is minimized at the clock frequency of 100MHz.

The work performed by Renukadevi and Rajambal [31] gives FPGA implementation of SVPWM technique for five-phase VSI. The SVPWM algorithm was presented as the high speed circuit for hardware coding and used over XILINX FPGA processor. The relationship of SVPWM with large, medium, and the combinations of both space vectors for five-phase VSI is analyzed. The experiment is performed over 1-hp  $5\phi$  induction motor under different SVPWM mechanisms. Later, the prominent SVPWM is identified with THD and output voltage.

Guzman et al. [32] have expressed the mechanism of load sharing in AC Micro-grids by using FPGA. This is based on frequency-locked-loop (FLL) and adaptive-linear-neuron (ADALINE). The experimental outcome mentions that the each VSI-control is used by implementing FPGA in micro-grid for proposition validity.

#### 4. **RESEARCH GAP**

The analysis outcome of the existing and recent researches idealizes that the realization mechanisms for VSI using various PWM mechanisms are more but failed to provide better performance and low hardware compatibility. The technique called SVPWM mechanisms offers better performance over different methods regarding torque ripple, better DC link utilization, lower THD, switching loss and easier digital system implementation. The SVPWM systems have been rapidly used, as it allows reducing commutation losses and output voltage harmonics, and obtaining higher amplitude MIs if compared with Sinusoidal PWM techniques. Currently, the digital control mechanisms have got more attention than the analog counterparts, as the increased performance and reliability of microprocessors. Most of the SVPWM mechanisms are performed by using the analog or digital circuits like microcontrollers and DSP. The studies which performed using digital mechanisms are rare and need a futuristic research towards the SVPWM using digital methods.

### 5. CONCLUSION

In this paper, the various aspects of the SVPWM in VSI are discussed. The SVPWM based mechanism offers the enhanced amplitude modulation indexes (MI) than sinusoidal PWM along with harmonics reduction and reduced communication losses. The existing SVPWM mechanisms are performed by the analog or digital circuits and FPGA. The FPGA SVPWM can offer more efficient and faster solution to tackle inverter related issues by functioning as analog and digital circuit and through which better realization can be achieved. This paper gives a prominent research survey in the SVPWM for  $3\varphi$  voltage source inverter (VSI) that includes the concept of VSI, SVPWM. The research survey represents the most recent researches in SVPWM and highlights the existing unresolved/research gap.

Also, the future line of researches for better realization of FPGA is described along with the order of future research. The future research can be followed with the following steps:-

- a. Perform the survey of existing researches for VSI, FPGA realization, and SVPWM techniques.

- b. Formulate the existing issues in the existing researches

- c. Design an FPGA-based system for realization of SVPWM in VSI.

- d. Perform the performance analysis of the system and compare with the other techniques

#### REFERENCES

- [1] N. Mohan, T. M. Undeland, W.P. Robbins, "Power Electronics: Converters, Applications, and Design", *John Wiley & Sons, Inc,* 1989

- [2] P. Milan & T. Green, "Control and filter design of three phase inverter for high power quality grid connection", *IEEE transactions on Power Electronics*, vol.18. pp.1-8, 2003

- [3] M. Dogan, M. Dursun, "Reduction of Asynchronous Motor Loss by Heuristic Methods (PSO-GA)", *Elektronika ir Elektrotechnika, vol.*117 (1), pp. 53-58, 2012

- [4] J. Sun, "Small-signal modeling of variable-frequency pulse-width modulators", *IEEE Trans.Aerosp. Electron. Syst*, vol. 38(3), pp. 1104–1108, 2002

[5] S. Araujo & F. Luiz, "*LCL fiter design for grid connected NPC inveters in offshore wind turbins*", 7th International

- [5] S. Araujo & F. Luiz, "*LCL fiter design for grid connected NPC inveters in offshore wind turbins*", 7th International conference on Power Electronics, pp. 1133-1138, 2007

- S.R Nandurkar, M. Rajeev, "Design and Simulation of three phase Inverter for grid connected Photovoltaic systems", Proceedings of Third Biennial National Conference, NCNTE, pp.80-83, 2012 M. Pradanovic & T. Green, "Control and filter design of three phase inverter for high power quality grid [6]

- [7] connection", IEEE transactions on Power Electronics, vol.18. pp.1-8, 2003

- J. Holtz, "Pulse Width Modulation A Survey", IEEE Transaction on Industrial Electronics, vol. 39, no. 5, pp. [8] 410-420, 1992

- J. Granado, R.G. Harley, G. Giana, "Understanding and Designing a Space Vector Pulse-Width-Modulator to [9] Control a Three Phase Inverter", *Transaction of the SAIEEE*, vol. 80, pp. 29-37, 1989 J. Holtz, "*Pulse Width Modulation for Electronic Power Conversion*", *Proceedings of the IEEE*, vol.82, no.8, pp.

- [10] 1194-1214, 1994

- V. Holms, D.G. "The Significance of Zero Space Vector Placements for Carrier-Based PWM Schemes", IEEE [11] Transactions on Industry Applications, vol. 32, no. 5, pp. 1122-1129, 1996

- S-L. An, "Study on the novel generalized discontinuous SVPWM strategies for three-phase voltage source inverters", *IEEE transactions on industrial informatics*, vol(9)2, pp.781-789, 2013 [12]

- M.A.A. Badran, A.M. Tahir, and W.F. Faris, "Digital Implementation of Space Vector Pulse Width Modulation Technique Using 8-bit Microcontroller", *World Applied Sciences Journal*, vol. 21, pp. 21-28, 2013 A. Boudouda, "Combined random space vector modulation for a variable speed drive using induction motor", [13]

- [14] Electrical Engineering, vol. 98(1), pp.1-15, 2016

- P. Chaudhari, "Space vector pulse width modulation (SVPWM) on DSP platform for utility grid synchronizable tie-line converter between AC-bus and DC-bus of a microgrid", Advancements in Power and Energy (TAP Energy), [15] International Conference on IEEE, 2015 M.M. Gaballah, "Design and Implementation of Space Vector PWM Inverter Based on a Low Cost

- M.M. Gaballah, [16]

- [17]

- M.M. Gaoanan, Design and Implementation of Space Vector 1 WM Inverter Based on a Low Cost Microcontroller", Arabian Journal for Science and Engineering, vol. 38.11, pp.3059-3070, 2013 M. Kassas and N. Ahmed, "Simulation and Implementation of Space Vector PWM Using Look-Up Table", Arabian Journal for Science and Engineering, vol.39 (6), pp.4815-4828, 2014 A.A. Kumar and D. Singh, "DSP based IFO control of HEV fed through impedance source inverter", Annual IEEE India Conference (INDICON), pp.1-6, 2013 C.S. Kumar, V. Gopelakrichnan, P. Dhanasekaran, P. Vaikundasalvan, "Digital Control of Space Vector Pulse [18]

- C.S. Kumar, V. Gopalakrishnan, R. Dhanasekaran, B. Vaikundaselvan, "Digital Control of Space Vector Pulse Width Modulation Based Shunt Active Filter", *Applied Mechanics and Materials*, vol.573, pp.115, 2014 M. Mirazimi, E. Babaei, and M.B.B. Sharifian, "Space vector PWM method for two-phase three-leg inverters", [19]

- [20]

- Power Electronics and Drive Systems Technologies Conference (PEDSTC), 2016. C. Piao and J.Y. Hung, "A simplified control strategy to balance dc-link capacitor voltage for multi-level diode clamped VSI based on discontinuous SVPWM", IEEE 24th International Symposium on Industrial Electronics [21] (ISIE). IEEE, 2015

- W. Promkhun and V. Kinnares, "Speed control of an asymmetrical type two-phase induction motor using discontinuous space vector pulse width modulation", Electrical Machines and Systems (ICEMS), 18th International [22] Conference, 2015

- [23] P. Sun, "Three-phase dual-buck inverter with unified pulsewidth modulation", IEEE Transactions on Power Electronics, vol. 27(3), pp.1159-1167, 2012

- C.d., Angel, and E.Todorovich, "High resolution FPGA DPWM based on variable clock phase shifting", IEEE [24] *Transactions on Power Electronics*, 25.5, pp. 1115-1119, 2010 [25] G. Oriti and A.L. Julian, "Three-phase VSI with FPGA-based multisampled space vector modulation", *IEEE*

- *transactions on industry applications*, vol. 47(4), pp.1813-1820, 2011 S. Pan, J. Pan, and Z. Tian, "A shifted SVPWM method to control DC-link resonant inverters and its FPGA realization", *IEEE Transactions on Industrial Electronics*, vol. 59(9), pp.3383-3391, 2012 [26]

- [27] R. Rajendran and N. Devarajan, "Analysis and FPGA Realization of a Pulse Width Modulator based on Voltage Space Vectors", *International Journal of Computer Applications*, vol.2(6), 2010

[28] M.D. Patil, D.Shah, and A.Kadam, "FPGA implementation of SVPWM control technique for three phase induction motor drive using fixed point realization", Circuits, Systems, Communication and Information Technology Applications (CSCITA), 2014 International Conference, 2014.

- B. Rashidi and M.Sabahi, "High Performance FPGA Based Digital Space Vector PWM Three Phase Voltage Source Inverter", *International Journal of Modern Education and Computer Science*, vol.5(1), pp.62, 2013 [29]

- [30]

- G. Renukadevi and K. Rajambal, "Field programmable gate array implementation of space-vector pulse-width modulation technique for five-phase voltage source inverter", *IET Power Electronics*, vol.7 (2), pp.376-389, 2014.

C. Guzman, A. Cardenas, and K. Agbossou, "Load Sharing Strategy for Autonomous AC Microgrids Based on FPGA Implementation of ADALINE&FLL", *IEEE Transactions on Energy Conversion*, vol.29 (3), pp. 663-672, 2014. [31] 2014

#### **BIOGRAPHIES OF AUTHORS**

Shalini Vashishtha obtained B.E from Government Engineering College Kota (University of Rajasthan), India. She completed M.Tech from M.S Ramaiah Institute of technology Bangalore, (VTU) India. Her areas of interest are HDL, VLSI design, Digital Electronics, Power Electronics. Currently she is pursuing Phd under Visvesvaraya Technological University, Belagavi. She is member of ISTE.

**Dr K.R. Rekha** obtained ME from Bangalore University, India in 2000. She isworking as a professor in the Department of Electronics and Communication in SJB Institute of Technology, Bangalore. She has done her PhD from Dr MGR University, Chennai. Her research interests include wireless communication, FPGA implementation, and Microcontroller and Embedded system design. She is a member of MIE, MISTE and IETE.